### Fakultät für Mathematik und Informatik Lehrgebiet Parallelität und VLSI

# Parallelisierung des Particle-in-cell-Codes PATRIC mittels GPU-Programmierung

### Diplomarbeit in Informatik

vorgelegt von:

Jutta Fitzek Im Oberen Rech 14 64823 Groß-Umstadt Matrikelnummer 7266545

Betreuer: Dr. Sabrina Appel

GSI Helmholtzzentrum für Schwerionenforschung

Erstgutachter: Prof. Dr. Jörg Keller

FernUniversität in Hagen

Zweitgutachter: Prof. Dr. Oliver Boine-Frankenheim

Technische Universität Darmstadt

Darmstadt, im September 2013

### Zusammenfassung

Auf Grund von Grenzen in der Weiterentwicklung der Computerhardware in Bezug auf die Geschwindigkeit und Forderungen nach der Lösung immer größerer Berechnungsprobleme spielen parallele Architekturen und Programmiermethoden eine immer wichtigere Rolle in der Informatik. Neben verteilter Verarbeitung werden auch immer häufiger lokale Ressourcen des einzelnen Knotens wie Grafikkarten für Datenparallelität genutzt. In der physikalischen Grundlagenforschung sind Simulationen häufig ressourcenintensiv und es wird nach Wegen gesucht, Berechnungen zu beschleunigen. Die vorliegende Diplomarbeit befasst sich mit einem sog. Particle-in-cell Verfahren, welches dazu genutzt wird, Teilchen in einem ringförmigen Teilchenbeschleuniger am GSI Helmholtzzentrum für Schwerionenforschung in Darmstadt zu simulieren. Es wird untersucht, wie ein bestehender Algorithmus, der bereits MPI verwendet, so abgeändert werden kann, dass zusätzlich zu der verteilten Berechnung auf den einzelnen Knoten lokal vorhandene Grafikprozessoren integriert werden können. Zum Einsatz kommen dabei NVIDIA GPUs, die mit Hilfe von CUDA C programmiert werden. Mehrere Modifikationen des Algorithmus werden diskutiert, erprobt und bewertet. Das Ergebnis dieser Arbeit ist ein modifizierter und gut wartbarer Algorithmus, der die aktuellen Simulationen schneller durchführen kann und als Basis für weitere Entwicklungen dienen wird. Des Weiteren werden die Möglichkeiten und Grenzen des Einbezugs der GPU aufgezeigt.

#### **Abstract**

Due to speed boundaries in computer hardware and demands to solve ever-growing computational problems, parallel architectures and programming methods play a more and more important role in computer science. Besides distributed computing techniques, local resources of the nodes such as GPUs are exploited for data parallelism. In physics research computer simulations are often resource-intense, and researchers seek for a speedup of their computations. This thesis deals with a particle-in-cell simulation code used to simulate particles in a circular particle accelerator at the GSI Helmholtzzentrum for Heavy Ion Research in Darmstadt, Germany. It is evaluated, how an existing algorithm that already uses MPI for parallelism can be modified in such a way, that additionally local GPUs on the distributed nodes can be integrated. NVIDIA GPUs are programmed using CUDA C. Several modifications of the present algorithm are discussed, tested and evaluated. The result of this thesis consists of a modified and well-maintainable algorithm that allows for a faster simulation and will be the basis for future development. Furthermore, the possibilities and limits of GPU integration are being elaborated.

# Inhaltsverzeichnis

| Ta | belle      | nverze   | ichnis                                       | vii    |

|----|------------|----------|----------------------------------------------|--------|

| A  | bbild      | ungsve   | erzeichnis                                   | ix     |

| Q  | uellte     | extverze | eichnis                                      | xi     |

| A  | bkürz      | zungen   | und Symbole                                  | xiii   |

| 1  | Einl       | eitung   |                                              | 1      |

|    | 1.1<br>1.2 |          | ration und Problemstellung                   | 1<br>3 |

| 2  | Gru        | ndlage   |                                              | 5      |

|    | 2.1        | Besch    | reibung der Teilchenbewegung                 | 6      |

|    |            | 2.1.1    | Physikalische Grundlagen                     | 6      |

|    |            | 2.1.2    | Simulation der Teilchenbewegung              | 7      |

|    | 2.2        | Parall   | elverarbeitung                               | 11     |

|    |            | 2.2.1    | Parallele Rechnerarchitekturen               | 11     |

|    |            | 2.2.2    | Modelle für Parallelrechner                  | 13     |

|    |            | 2.2.3    | Maße für Parallelität                        | 15     |

|    |            | 2.2.4    | Entwurf paralleler Algorithmen               | 17     |

|    |            | 2.2.5    | Parallele Softwareentwicklung                | 21     |

|    | 2.3        | Parall   | elität mit Hilfe von Grafikprozessoren       | 24     |

|    |            | 2.3.1    | Historie                                     | 24     |

|    |            | 2.3.2    | Programmierkonzepte                          | 25     |

|    |            | 2.3.3    | Aufbau einer Grafikkarte                     | 26     |

|    |            | 2.3.4    | Softwareentwicklung                          | 30     |

|    |            | 2.3.5    | Theoretische Einordnung                      | 34     |

|    | 2.4        | Mathe    | ematische Genauigkeit von Grafikprozessoren  | 35     |

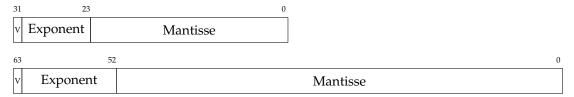

|    |            | 2.4.1    | Darstellung von Gleitkommazahlen             | 36     |

|    |            | 2.4.2    | Fehlerbetrachtung                            | 36     |

| 3  | Sim        | ulation  | n mit den bestehenden Particle-in-cell Codes | 41     |

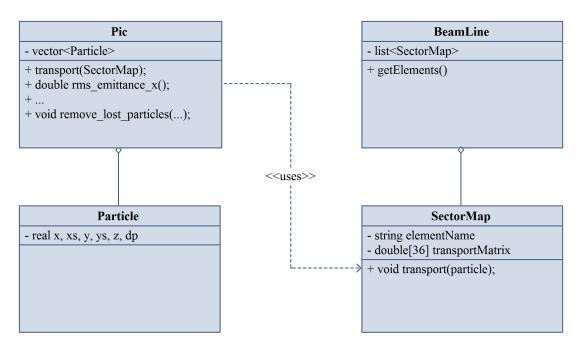

|    | 3.1        | Das Si   | imulationsprogramm PATRIC                    | 41     |

|    |            | 3.1.1    | Übersicht und Aufbau                         | 41     |

|    |            | 3.1.2    | Ablauf einer Teilchensimulation              | 43     |

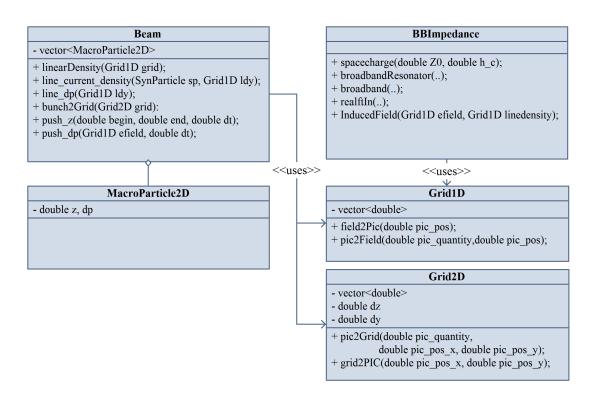

|    | 3.2        | Das Si   | imulationsprogramm LOBO                      | 45     |

|    |            | 3.2.1    | Übersicht und Aufbau                         | 45     |

|    |      | 3.2.2     | Ablauf einer Teilchensimulation                 | 45  |

|----|------|-----------|-------------------------------------------------|-----|

| 4  | Para | allelisie | erungsstrategien anderer Particle-in-cell Codes | 49  |

|    | 4.1  | Einsat    | z von GPUs im Simulationsprogramm ELEGANT       | 49  |

|    |      | 4.1.1     | Parallelisierung mit MPI                        | 50  |

|    |      | 4.1.2     | Parallelisierung mit GPUs                       | 51  |

|    |      | 4.1.3     | Bewertung                                       | 53  |

|    | 4.2  | Einsat    | z von GPUs im Simulationsprogramm PIConGPU      | 55  |

|    |      | 4.2.1     | Parallelisierung mit MPI                        | 55  |

|    |      | 4.2.2     | Parallelisierung mit GPUs                       | 56  |

|    |      | 4.2.3     | Bewertung                                       | 57  |

|    | 4.3  |           | z von GPUs in anderen Simulationsprogrammen     | 58  |

| 5  | Mod  | difikati  | on des Particle-in-cell Codes                   | 61  |

|    | 5.1  |           | cklungsumgebung                                 | 62  |

|    | 5.2  |           | rändertes PATRIC Programm                       | 63  |

|    | ٠    | 5.2.1     | · · · · · · · · · · · · · · · · · · ·           | 63  |

|    | 5.3  |           | erlegungen zum Einbezug der GPU                 | 65  |

|    | 0.0  | 5.3.1     | Verwendete Datenstrukturen                      | 65  |

|    |      | 5.3.2     | Verwendeter Speicher für statische Daten        | 66  |

|    |      | 5.3.3     | Verwendeter Speicher für dynamische Daten       | 67  |

|    | 5.4  |           | ng mit PATRIC                                   | 68  |

|    | 0.1  | 5.4.1     | Einfacher Ansatz, Transportschritt auf der GPU  | 69  |

|    |      | 5.4.2     | Teilchen auf der GPU halten                     | 71  |

|    |      | 5.4.3     | Ausgabe von Zwischenergebnissen                 | 74  |

|    |      | 5.4.4     | Berechnung von Strahlgrößen auf der GPU         | 76  |

|    |      | 5.4.5     | Gleitkommadarstellung und Genauigkeit           | 79  |

|    | 5.5  |           | ctive Effekte                                   | 80  |

|    | 5.5  | 5.5.1     | Messungen mit dem Originalprogramm LOBO         | 80  |

|    |      | 5.5.2     | Interpolation mit atomaren Operationen          | 81  |

|    |      | 5.5.3     | Interpolation mit Vorsortierung                 |     |

|    | 5.6  |           | ation der vorgenommenen Parallelisierungen      | 84  |

|    | 5.7  | Finho     | ziehung mehrerer MPI-Knoten                     |     |

|    | 5.7  | Linber    | zienung memerer im r-knoten                     | 65  |

| 6  | Dis  | kussior   | 1                                               | 87  |

|    | 6.1  | Zusan     | nmenfassung und Bewertung der Ergebnisse        | 87  |

|    | 6.2  | Ausbl     | ick                                             | 89  |

| Aı | nhan | g         |                                                 | 91  |

|    | A    | Progra    | ammierung                                       | 91  |

|    |      | A.1       | Übersicht über die CUDA C Spracherweiterungen   | 91  |

|    |      | A.2       | Zeitmessung                                     | 92  |

|    |      | A.3       | Programmauszüge                                 | 93  |

|    | В    | Forme     | 8                                               | 104 |

|    |      | B.1       | Transportmatrizen                               |     |

|    |      | B 2       | 1                                               | 105 |

| Simulationsprogramme                 | . 106 |

|--------------------------------------|-------|

|                                      |       |

| C.2 Die Konfigurationsdatei von LOBO | . 107 |

| Inhalt der beigefügten DVD           | . 108 |

| urverzeichnis                        | 109   |

| ndigkeitserklärung                   | 115   |

|                                      |       |

# **Tabellenverzeichnis**

| 5.1 | Spezifikation der verwendeten Grafikkarte                             | 62 |

|-----|-----------------------------------------------------------------------|----|

| 5.2 | Transportschritt auf der GPU: Koordinate oder Teilchen pro Thread     | 70 |

| 5.3 | Teilchen auf der GPU: Vergleich Anzahl Threads pro Block              | 71 |

| 5.4 | Teilchen auf der GPU: Laufzeitvergleich bei 50% Teilchenverlust       | 73 |

| 5.5 | Teilchen auf der GPU: Laufzeitvergleich bei der Nutzung von Streams . | 75 |

| 5.6 | Teilchen auf der GPU: Vergleich einfache und doppelte Genauigkeit     | 79 |

| 5.7 | Teilchen und Gitter auf der GPU: Laufzeiten der einzelnen Schritte    | 82 |

| 5.8 | Teilchen und Gitter auf der GPU: Vergleich Gittergrößen               | 83 |

| 5.9 | Teilchen und Gitter auf der GPU: Vergleich mit Vorsortierung          | 84 |

# Abbildungsverzeichnis

| 2.1  | beschreibung der Teilchen eines Teilchenpakets                                                                         | ð  |

|------|------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Berechnungszyklus einer PIC-Simulation                                                                                 | 10 |

| 2.3  | Shared-memory Modell, das auch der PRAM zu Grunde liegt                                                                | 14 |

| 2.4  | Schritte beim Entwurf paralleler Algorithmen                                                                           | 18 |

| 2.5  | EVA-Prinzip vor dem Hintergrund der Parallelverarbeitung                                                               | 23 |

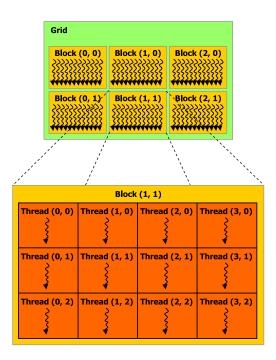

| 2.6  | CUDA Ausführungsmodell                                                                                                 | 26 |

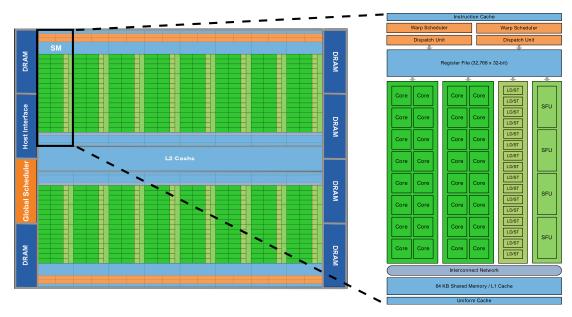

| 2.7  | Aufbau einer Tesla C2075 Grafikkarte                                                                                   | 27 |

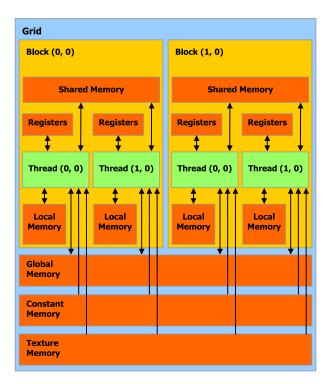

| 2.8  | CUDA Speichermodell                                                                                                    | 29 |

| 2.9  | Gleitkommazahlen einfacher und doppelter Genauigkeit                                                                   | 36 |

| 3.1  | Objekte des PATRIC Simulationsprogramms                                                                                | 42 |

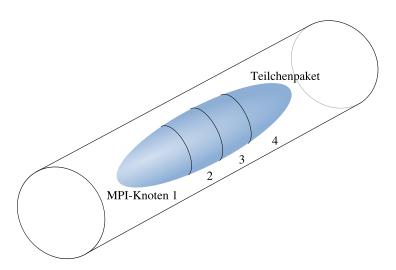

| 3.2  | Aufteilung der Teilchen auf MPI-Knoten in PATRIC                                                                       | 43 |

| 3.3  | Objekte des LOBO Simulationsprogramms                                                                                  | 46 |

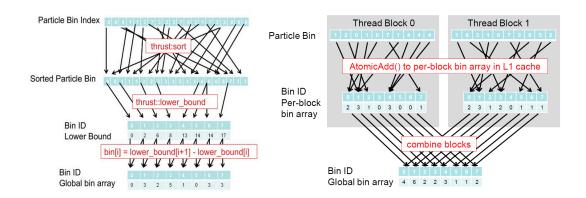

| 4.1  | Interpolation im Programm ELEGANT                                                                                      | 52 |

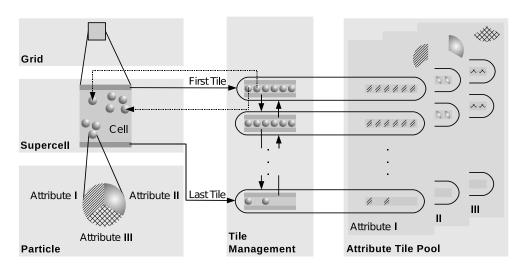

| 4.2  | Datenzerlegung im Programm PIConGPU                                                                                    | 56 |

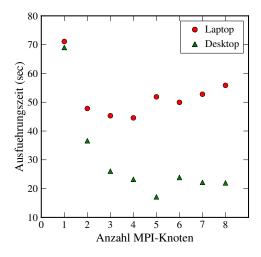

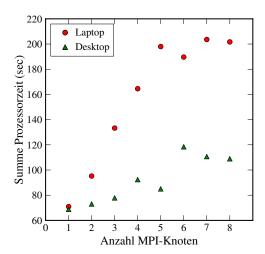

| 5.1  | Ausführungszeit des Originalprogramms PATRIC                                                                           | 64 |

| 5.2  | Prozessorzeit des Originalprogramms PATRIC                                                                             | 64 |

| 5.3  | Darstellung der Teilchen als Strukturen oder Arrays                                                                    | 65 |

| 5.4  | Ausgabe des Profilers zum Originalprogramm PATRIC                                                                      | 68 |

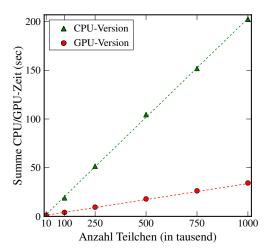

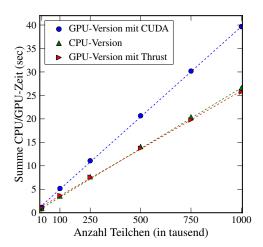

| 5.5  | Vergleich Modifikation in PATRIC: Teilchen auf der GPU halten                                                          | 72 |

| 5.6  | Vergleich Modifikation in PATRIC: Variierung der Ausgabeschritte                                                       | 74 |

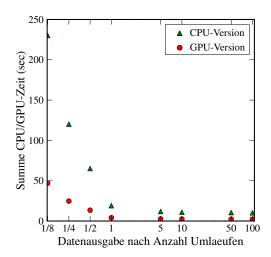

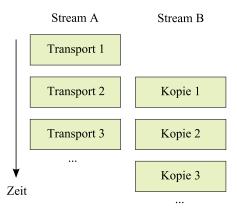

| 5.7  | Vergleich Modifikation in PATRIC: Überlappende Ausgabe mit Streams                                                     | 75 |

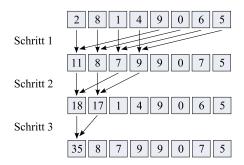

| 5.8  | Schema der Reduktion mittels sequentieller Adressierung                                                                | 77 |

| 5.9  | $\label{thm:continuous} Vergleich Modifikation in PATRIC: Emittanzermittlung auf der GPU  .  .  .  .  .  .  .  .  .  $ | 78 |

| 5.10 | Ausgabe des Profilers zum Originalprogramm LOBO                                                                        | 80 |

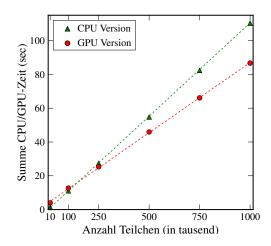

| 5.11 | Vergleich Modifikation in LOBO: Interpolation mit atomaren Operationen                                                 | 82 |

# Quelltextverzeichnis

| 2.1        | Thrust Beispielaufruf                                                                                                   | 33       |

|------------|-------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1<br>3.2 | PATRIC Originalversion: Zentrale Schleife des Teilchentransports LOBO Originalversion: Zentrale Schleife der Berechnung | 44<br>47 |

| 5.1<br>5.2 | PRAM Pseudocode: Transportschritt auf der GPU                                                                           | 69<br>76 |

| A.1        | Zeitmessung der CPU-Programmausführung                                                                                  | 92       |

| A.2        |                                                                                                                         | 92       |

|            |                                                                                                                         | 93       |

|            | PATRIC: Transportschritt auf der GPU, konstanter Speicher                                                               |          |

| A.5        | PATRIC: Teilchendaten auf der GPU, Datenstruktur                                                                        | 95       |

| A.6        | Nutzung von Streams: Definition und Verwendung                                                                          | 96       |

| A.7        | Berechnung der Emittanz auf der GPU mit CUDA                                                                            | 97       |

| A.8        | Berechnung der Emittanz auf der GPU mit Thrust                                                                          | 99       |

| A.9        | LOBO: Kernel zur Bewegung der Teilchen                                                                                  | 00       |

| A.10       | LOBO: Interpolation, Variante mit atomaren Operationen                                                                  | 01       |

| A.11       | LOBO: Variante mit Sortierung, Sortiermechanismus                                                                       | 02       |

| A.12       | LOBO: Variante mit Sortierung, Interpolation                                                                            | 03       |

## Abkürzungen und Symbole

FAIR Facility for Antiproton and Ion Research

GSI GSI Helmholtzzentrum für Schwerionenforschung GmbH

LOBO Longitudinal Beam Dynamics Simulations Code, Abteilung Strahl-

physik, GSI

PATRIC PArticle TRackIng Code, Abteilung Strahlphysik, GSI

ELEGANT ELEctron Generation ANd Tracking Programm, Argonne National

Laboratory, USA

PIConGPU Particle in Cell Code on the GPU, Helmholtz-Zentrum Dresden-

Rossendorf

CUDA Compute Unified Device Architecture, eine von NVIDIA entwickelte

parallele Architektur für die Grafikverarbeitung

cuFFT FFT-Bibliothek für die GPU von NVIDIA

EVA Eingabe-Verarbeitung-Ausgabe, Prinzip der rechnergestützten Da-

tenverarbeitung

GPU Graphics Processing Unit, Grafikprozessor

MPI Message Passing Interface, Standard für den Nachrichtenaustausch

in verteilten Computersystemen

PIC Particle-in-cell Verfahren

PRAM Parallel Random Access Machine, Modell für einen Parallelrechner

B Magnetisches Feld E Elektrisches Feld

*e* Elektrische Elementarladung ( $e = 1.6022 \cdot 10^{-19}C$ )

F Lorentzkraft

$\epsilon$  Emittanz

## 1 Einleitung

Auf Grund von wachsenden Anforderungen zur Lösung immer größerer Berechnungsprobleme aber andererseits dem Erreichen von Grenzen in der Weiterentwicklung der Computerhardware spielen parallele Architekturen und Programmiermethoden eine immer größere Rolle in der Informatik. Neben verteilter Verarbeitung werden auch immer häufiger lokale Ressourcen wie Grafikkarten für Datenparallelität genutzt.

Ziel der vorliegenden Diplomarbeit ist es, bestehende Programme zur Simulation von Teilchen in einem Teilchenbeschleuniger unter Einsatz von Grafikkartenprogrammierung zu parallelisieren.

### 1.1 Motivation und Problemstellung

In der physikalischen Grundlagenforschung sind Simulationen häufig sehr ressourcenintensiv und es wird nach Wegen gesucht, Berechnungen zu beschleunigen. Die vorliegende Diplomarbeit befasst sich mit bestehenden Programmen, die dazu genutzt werden, Teilchen in einem ringförmigen Teilchenbeschleuniger am GSI Helmholtzzentrum für Schwerionenforschung GmbH (GSI) in Darmstadt zu simulieren.

Teilchenbeschleuniger werden in der Forschung, in der Medizin und auch in der Industrie weltweit eingesetzt. In der physikalischen Grundlagenforschung dienen sie dazu, den Aufbau der Materie zu erforschen. Simulationen spielen zur Beschreibung der Teilchenbewegung eine essentielle Rolle, um Effekte mit vorgegebenen Parametern speziell untersuchen zu können. Simuliert wird dabei über die Zeit oder den Weg der Teilchenbewegung, welche ihrerseits durch den Aufbau des Beschleunigers und durch Effekte der Teilchen untereinander und mit ihrer Umgebung bestimmt ist.

Ziel ist einerseits das Verstehen der Teilchenbewegung in der bestehenden Beschleunigeranlage, hierbei werden die Ergebnisse der Simulationen den real gemessenen Größen gegenübergestellt. Andererseits werden im Rahmen der Entwicklung neuer Teilchenbeschleuniger auch Simulationen für noch nicht gebaute Beschleunigeranlagen durchgeführt. Im Rahmen eines internationalen Projekts entsteht aktuell unter dem Namen Facility for Antiproton and Ion Research (FAIR) eine neue internationale Beschleunigeranlage zur Forschung mit Antiprotonen und Ionen, für die die bestehende GSI Beschleunigeranlage als Injektor dient. In diesem Zusammenhang werden weitreichende Simulationen durchgeführt, deren Ergebnisse Eingang in die Bauplanung finden.

Für die genannten Simulationen wird das Particle-in-cell (PIC) Programm PATRIC (Particle Tracking Code) verwendet. Das Simulationsprogramm wurde in der Abteilung Strahlphysik der GSI entwickelt und ist speziell auf die Fragestellungen zugeschnitten, die sich an den Beschleunigeranlagen der GSI ergeben. Trotz einer Konzentration auf die relevanten Fragestellungen und eines modernen, strukturierten Programms können sich allein auf Grund der zu simulierenden Teilchenmengen und Betrachtungszeiträume lange Simulationsdauern ergeben. Der Wunsch nach einer Beschleunigung der Simulationen ist dabei nicht neu. Im bestehenden Programm PATRIC sind bereits seit 2001 Mechanismen zur verteilten parallelen Berechnung mittels Message Passing Interface (MPI) eingebaut. Damit ist es möglich, die betrachtete Teilchenmenge aufzuteilen und von mehreren Knoten parallel bearbeiten zu lassen, was bei allen länger laufenden Simulationen im Rahmen der vorhandenen Rechnerressourcen auch genutzt wird (typischerweise mit 4-16 Berechnungsknoten). Trotz des Einsatzes von MPI können lang laufende Simulationen mehrere Stunden dauern. Der Wunsch ist deshalb, die Berechnungen auf den einzelnen verteilten Berechnungsknoten weiter zu beschleunigen, um Simulationsergebnisse insgesamt frühzeitiger vorliegen zu haben.

Aktuell werden in der Industrie und in der Forschung zur Unterstützung von rechenintensiven Berechnungen vermehrt Grafikprozessoren (GPUs) eingesetzt. Diese versprechen einen gegenüber einem herkömmlichen Prozessor stark verbesserten Durchsatz bei der massenhaften Ausführung immer gleicher Gleitkomma-Berechnungen mit verschiedenen Daten, so wie es z. B. bei Simulationen vieler Teilchen der Fall ist. In der Forschung gibt es aus diesem Grund mehr und mehr Projekte, die vorhandene Berechnungen auf Grafikkarten portieren; in der Industrie gibt es bereits viele Anwendungen, die für berechnungsintensive Aufgaben Grafikkarten nutzen. Vor diesem Hintergrund entstand in der Abteilung Strahlphysik die Idee, Teile des Simulationsprogramms PATRIC auf Grafikkarten zu portieren, um eine weitere Verkürzung der Simulationsdauer zu erzielen.

Dazu war es Aufgabe im Rahmen der Diplomarbeit zu untersuchen, wie die bestehenden Simulationsprogramme so abgeändert werden können, dass zusätzlich auf den einzelnen MPI-Knoten eine lokal vorhandene Grafikkarte integriert werden kann. Neben dem Programm PATRIC, bei dem einzelne ausgewählte Teile auf die GPU portiert wurden, wird auch das ebenfalls von der Abteilung Strahlphysik entwickelte Programm LOBO (Longitudinal Beam Dynamics Simulations Code) betrachtet, bei dem ein größerer Anteil auf die GPU portiert wurde. Als Vorarbeit wurden dabei zunächst an Hand anderer Simulationsprogramme, die bereits eine GPU-Unterstützung enthalten, generelle Möglichkeiten zur Einbindung von Grafikkarten ermittelt.

Für die eigenen Implementierungen war als Laufzeitumgebung eine Grafikkarte des Herstellers NVIDIA vorgegeben. Die Präferenz für NVIDIA im Umfeld der Teilchensimulationen an der GSI ist vor allem in der breiten Unterstützung durch frei verfügbare Bibliotheken (wie cuFFT, cuBLAS etc.) begründet. Die Ausführungen im Grundlagenkapitel und die Implementierungen im praktischen Teil der Arbeit konzentrieren sich aus diesem Grund auf NVIDIA Grafikkarten; die Änderungen an den bestehenden Simulationsprogrammen wurden mit CUDA C implementiert.

Im Rahmen der Arbeit werden mehrere Modifikationen des bestehenden Algorithmus vorgeschlagen, diskutiert, getestet und gemessen. Das Ergebnis dieser Arbeit ist ein modifizierter Algorithmus, der die aktuellen Simulationen schneller durchführen kann und als Basis für weitere Entwicklungen dienen wird. Des Weiteren werden die Möglichkeiten und Grenzen des Einbezugs der GPU aufgezeigt.

### 1.2 Aufbau der Arbeit

Kapitel 2 behandelt die Grundlagen, auf denen diese Arbeit aufbaut. Es wird zunächst auf die Simulation von Teilchen in Beschleunigern eingegangen, soweit es zum Verständnis der Arbeit erforderlich ist. Es folgt eine detaillierte Darstellung der Grundkonzepte der Parallelisierung und der im Rahmen dieser Arbeit eingesetzten Methoden. Einen Schwerpunkt bildet dabei am Ende des Kapitels die Betrachtung von Grafikprozessoren.

In Kapitel 3 werden die betrachteten Teilchensimulationsprogramme PATRIC und LOBO in ihrer bestehenden Version beschrieben. Es wird als Überleitung zum praktischen Teil der Arbeit angedeutet, an welchen Stellen generell Parallelisierungsmöglichkeiten bestehen.

In Kapitel 4 werden zur Darstellung des aktuellen Stands der Forschung der Einsatz von Grafikprozessoren in anderen Teilchensimulationsprogrammen beleuchtet.

Den Schwerpunkt dieser Arbeit bildet die Einbindung der GPU in die bestehenden Simulationsprogramme. In Kapitel 5, dem Kernstück der Arbeit, werden deshalb verschiedene Modifikationen der Programme PATRIC und LOBO betrachtet. Dabei werden Möglichkeiten untersucht, die GPU möglichst optimal auf das vorliegende Problem zugeschnitten einzusetzen. Die verschiedenen Modifikationen werden jeweils vorgeschlagen und theoretisch diskutiert; anschließend werden die gewonnenen Messergebnisse vorgestellt und bewertet. Ein kurzer Ausblick am Ende des Kapitels befasst sich mit der Einbeziehung der verteilten Berechnung mittels MPI, welche vorher ausgeklammert wurde.

Das Ende der Arbeit bildet eine abschließende Zusammenfassung und Bewertung der Ergebnisse in Kapitel 6. Vor diesem Hintergrund wird am Schluss ein Ausblick auf zukünftige Weiterentwicklungen gegeben.

## 2 Grundlagen

Zur Simulation der Teilchenbewegung im Beschleuniger werden am GSI Helmholtzzentrum für Schwerionenforschung GmbH (GSI) selbst entwickelte Programme genutzt. Die damit durchgeführten Simulationen spielen für das physikalische Verständnis der Strahlphysik eine bedeutende Rolle und zeitnahe Ergebnisse der Simulationsläufe sind dabei eine wichtige Voraussetzung. Im Rahmen dieser Arbeit soll untersucht werden, wie die Programme und damit die implementierten Algorithmen unter Einsatz von Grafikkartenprogrammierung parallelisiert werden können.

Als Grundlage ist es wichtig zu verstehen, was Gegenstand der Simulationen ist. Als erstes wird deshalb kurz die dahinterstehende Physik skizziert. Ausgehend von der Beschreibung der Teilchenbewegung in einem Beschleuniger wird erklärt, wie die Teilchen selbst und die Beschleunigerelemente in den Simulationen abgebildet werden. Darauf aufbauend wird auf den generellen Ablauf einer Teilchensimulation eingegangen.

Als Basis für die Implementierung ist es zunächst notwendig, auf die Grundlagen der Parallelisierung einzugehen. Aufbauend auf parallelen Rechnerarchitekturen wird das verwendete Modell für Parallelrechner vorgestellt und die genutzten Messgrößen für parallele Programme erläutert. Als Basis für die parallele Softwareentwicklung wird die Methode zum Entwurf paralleler Algorithmen vorgestellt, die im Rahmen der eigenen Implementierungen eingesetzt wurde. Ein kurzer Abschnitt zu MPI (Message Passing Interface) bildet die Grundlage zum Verständnis der bereits im Programm PATRIC bestehenden Ansätze zur Parallelisierung.

Ziel dieser Arbeit ist die Einbindung der Grafikkarte in die Berechnungen. Um die dadurch bestehenden Möglichkeiten der Parallelisierung zu verstehen, müssen die mit der Grafikkarte verbundenen Programmierkonzepte betrachtet werden. Vorgestellt wird als Basis der Aufbau einer NVIDIA Grafikkarte mit Fokus auf die vorhandenen Ausführungseinheiten und der Speicherhierarchie. Darauf aufbauend wird das mit CUDA (Compute Unified Device Architecture) zur Verfügung stehende Programmiermodell dargestellt, das als Grundlage für die Parallelisierung dient. Vor diesem Hintergrund wird auf einzelne Aspekte der Programmierung eingegangen, die im Rahmen des praktischen Teils eine Rolle spielen.

Ein Randthema bildet die Fragestellung nach der Genauigkeit der durchgeführten Simulationen im Hinblick auf den Einsatz von Grafikkarten, weshalb im Rahmen der Grundlagen die Gleitkommadarstellung in Rechnern und die damit verbundene mögliche Fehlerfortpflanzung angesprochen wird.

### 2.1 Beschreibung der Teilchenbewegung

### 2.1.1 Physikalische Grundlagen

Bevor auf die Simulation mit der Particle-in-cell Methode eingegangen wird, soll zunächst kurz die dahinterstehende Physik erläutert werden, insofern es für das Verständnis der Arbeit notwendig erscheint. Dazu wird den Ausführungen in [Wil96] gefolgt.

In einem Teilchenbeschleuniger werden Teilchen mit Hilfe von elektromagnetischen Kräften beschleunigt und auf der gewünschten Bahn gehalten. Ein Teilchen besitzt die Ladung  $q = Z \cdot e$ , dem Produkt aus der Ladungszahl Z und der Elementarladung e. Wenn dieses elektrisch geladene Teilchen mit der Geschwindigkeit  $\overrightarrow{v}$  einen Raum durchfliegt, in dem das magnetische Feld  $\overrightarrow{B}$  und das elektrische Feld  $\overrightarrow{E}$  herrschen, wirkt auf das Teilchen die Lorentzkraft

$$\overrightarrow{F} = q \cdot (\overrightarrow{v} \times \overrightarrow{B} + \overrightarrow{E}). \tag{2.1.1}$$

Das elektrische Feld ermöglicht eine Energieänderung und damit eine Beschleunigung der Teilchen in longitudinaler Strahlrichtung. Das magnetische Feld hat eine transversale, rein ablenkende bzw. bahnführende Wirkung, da das magnetische Feld senkrecht zur Bewegungsrichtung des Teilchens steht [vgl. Wil96, S. 3f.]. N gleichartige Teilchen bilden dabei den Teilchenstrahl, der entweder gleichförmig ist oder in Teilchenpakete aufgeteilt vorliegt.

Der Schwerpunkt der Untersuchungen in der Abteilung Strahlphysik liegt auf Kreisbeschleunigern. Einfache Kreisbeschleuniger besitzen viele Magnete, um die Teilchen transversal abzulenken und somit auf ihrer Bahn zu halten und eine Hochfrequenzanlage, um die Teilchen longitudinal zu beschleunigen. Bei dem bei der GSI vorhandenen Kreisbeschleuniger handelt es sich um ein sog. Synchrotron. Wie der Name andeutet, muss bei diesem Beschleunigertyp das Magnetfeld synchron mit der Energie hochgefahren werden, um die Teilchen während ihrer Beschleunigung auf der Bahn zu halten [vgl. Wil96, S. 23ff.]. Daneben gibt es an der GSI einen Speicherring. Dieser arbeitet nach demselben Prinzip, jedoch werden hierbei die Teilchen über einen längeren Zeitraum gespeichert und evtl. sogar abgebremst. Im Rahmen des Aufbaus der neuen FAIR-Anlage werden bei der GSI weitere Kreisbeschleuniger hinzukommen, diese sind bereits jetzt Gegenstand der Betrachtungen.

Im Rahmen der Diplomarbeit wurde in drei Schritten zuerst als Schwerpunkt der Aspekt der transversalen Teilchenbewegung behandelt, danach wurde die longitudinale Bewegung der Teilchen betrachtet sowie abschließend Überlegungen zur gesamten Teilchenbewegung angestellt.

Um die transversale Bewegung der Teilchen zu verstehen, müssen die magnetischen Felder betrachtet werden. Magnetische Kräfte in einem Beschleuniger werden durch starke Magnete wie Dipole, Quadrupole, Sextupole und Oktupole erzeugt, welche im Beschleuniger eingebaut sind. Diese Magnete haben einen Einfluss auf die transversale

Teilchenbewegung, der sich durch die Methoden der Optik beschreiben lässt, weshalb dabei auch von "Strahloptik" gesprochen wird. Dipole dienen dazu, Teilchen in einem Kreisbeschleuniger auf der Kreisbahn zu halten. Quadrupole kann man sich als optische Linsen vorstellen; sie dienen der Fokussierung von Teilchen, wobei sie nur in einer Ebene fokussieren (und in der anderen defokussieren). Sextupole und Oktupole dienen zur Kompensation von Abweichungen. Die Struktur der Anordnung der Magnete im Beschleuniger (engl. "lattice") ist typischerweise symmetrisch, wobei sich fokussierende und ablenkende Magnete abwechseln. Diese Anordnung ist Grundlage für die Berechnung der transversalen Teilchenbewegung. Im Rahmen der Arbeit wurden idealtypische Beschleunigerkomponenten in Form einer vereinfachten linearen Strahloptik (d. h. nur mit Dipolen und Quadrupolen) verwendet.

Um die longitudinale Teilchenbewegung zu verstehen, kann man sich die Bewegung eines ganzen Teilchenpakets auf einer elektromagnetischen Welle vorstellen. Ein Teilchen besitzt eine gewisse Frequenz und Phase und erhält beim Durchlaufen der Hochfrequenzanlage eine bestimmte Energie [vgl. Hin08, S. 308]. Teilchen mit einer Impulsabweichung sehen bei ihrem Eintreffen eine andere Phase und erhalten so weniger oder mehr Energie als das synchrone Teilchen. Die Teilchen nähern sich im Folgenden der Sollphase an und führen Schwingungen um diese aus. Bei kleinen Schwingungsamplituden können diese Phasen- und damit Energieschwingungen durch einen harmonischen Oszillator beschrieben werden. Bei zu großen Schwingungsamplituden wird der stabile Bereich verlassen und die Teilchen gehen verloren [vgl. Hin08, S. 311].

Bisher wurden äußere elektromagnetische Felder beschrieben, die auf die Teilchen einwirken. Daneben existieren auch elektromagnetische Selbstfelder, die durch die Teilchen untereinander und in der Verbindung mit dem umgebenden Beschleuniger erzeugt werden [vgl. Rei08, S. 163ff.]. Die Effekte dieser Felder werden kollektive Effekte genannt. In der physikalischen Betrachtung werden sie in ihre Einzelkomponenten aufgeteilt. Die Stärke dieser Felder hängt von der Teilchendichte ab und ist umso größer, je niedriger die Energie und je höher die Teilchendichte ist [vgl. Hin08, S. 27]. Die Effekte dieser Felder können zu einem Auseinanderdriften der Teilchenbahnen und damit einer Defokussierung des Strahls und einem Anwachsen der Emittanz führen und sogar schlimmstenfalls den gesamten Strahl destabilisieren. Da es gerade im Hinblick auf die neue FAIR-Anlage auf hohe Strahlintensitäten ankommt, müssen diese Effekte genau untersucht werden und spielen deshalb bei den Simulationen eine wichtige Rolle.

### 2.1.2 Simulation der Teilchenbewegung

Die Simulation der Teilchenbewegung dient dazu, theoretische Annahmen zu überprüfen, Experimente vorzubereiten oder auch zukünftige Beschleunigeranlagen zu entwerfen. Betrachtet werden dabei Makroteilchen, die viele einzelne Teilchen repräsentieren<sup>1</sup>. Ein Teilchen wird dabei relativ zum vorher erwähnten synchronen Teilchen betrachtet. Das synchrone Teilchen ist das zentrale Teilchen eines Teilchenpakets und

$<sup>^1</sup>$ Im Folgenden wird dennoch von Teilchen gesprochen, obwohl eigentlich Makroteilchen gemeint sind.

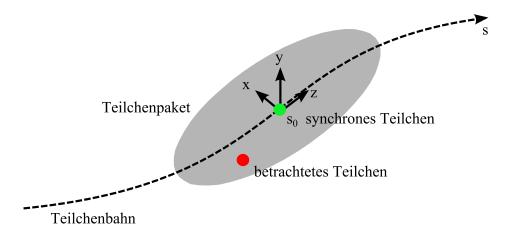

Abbildung 2.1: Die betrachteten Teilchen eines Teilchenpakets werden durch ihre Koordinaten in Bezug auf das synchrone Teilchen beschrieben.

bewegt sich auf der Idealbahn (oder auch Sollbahn) durch den Beschleuniger [vgl. Hin08, S. 117]. Die Idealbahn ist durch die Energie des Teilchens sowie die Stärke der ablenkenden Dipole bestimmt.

Die Position eines Teilchens im Beschleuniger wird durch ein mitbewegtes Koordinatensystem beschrieben, dessen Ursprung sich an der aktuellen Position des synchronen Teilchens auf der Idealbahn befindet. Die x-Achse zeigt horizontal zur Strahlrichtung nach links, die y-Achse stellt die auf der Teilchenbahn vertikal stehende Achse dar, die z-Achse ist die Tangentialachse entlang der Strahlrichtung, siehe Abb. 2.1. Dabei werden x und y als transversale Koordinaten und z als longitudinale Koordinate bezeichnet.

Ein einzelnes Teilchen wird durch einen 6-komponentigen Vektor beschrieben

$$v(s) = \begin{pmatrix} x \\ x' \\ y \\ y' \\ z \\ v \end{pmatrix}$$

(2.1.2)

mit x und x' als horizontale Orts- und Richtungsabweichung, y und y' als vertikale Orts- und Richtungsabweichung, z als longitudinale Ortsabweichung und v als Implusabweichung im Vergleich zum synchronen Teilchen. In Einheiten werden x, y, v in mm, x', y' in mrad und v in Promille ausgedrückt [vgl. Hin08, S. 122].

Auf dem Weg durch den Beschleuniger üben die eingebauten Magnete Kräfte auf die Teilchen aus. Diese lassen sich als Transformation des Teilchenvektors ausdrücken. Dabei wird das Koordinatensystem mit Hilfe von Matrizen transformiert, mathematisch handelt es sich um Transfermatrizen, in der Strahlphysik spricht man hingegen von Transportmatrizen, um auf den Transport der Teilchen durch den Beschleuniger

hinzuweisen. Auch hier soll im Folgenden von Transportmatrizen die Rede sein. Eine entsprechende Herleitung des Matrixformalismus findet sich bei [Hin08, S. 123ff.].

Die Bewegung eines Teilchens entlang des Rings wird als Transformation des Teilchenvektors v durch die Transportmatrizen M der durchlaufenen Magnete dargestellt. Das Ergebnis bildet dann die neue Position und Bewegungsrichtung des Teilchens

$$v' = M \cdot v \tag{2.1.3}$$

wobei die Transportmatrix M die Grundform für die lineare Optik

$$M = \begin{pmatrix} M_{11} & M_{12} & 0 & 0 & 0 & M_{16} \\ M_{21} & M_{22} & 0 & 0 & 0 & M_{26} \\ 0 & 0 & M_{33} & M_{34} & 0 & 0 \\ 0 & 0 & M_{43} & M_{44} & 0 & 0 \\ M_{51} & M_{52} & 0 & 0 & 1 & M_{56} \\ 0 & 0 & 0 & 0 & 0 & 1 \end{pmatrix}$$

(2.1.4)

besitzt. Die beiden quadratischen Untermatrizen stellen die eigentliche transversale Abbildung (radial und axial) dar. Die Elemente  $M_{16}$  und  $M_{26}$  stellen die Orts- und Winkeldispersion dar, da durch eine Ablenkung auch immer eine Aufspaltung der Teilchenbahnen wie durch ein Prisma erfolgt. Die Elemente  $M_{51}$ ,  $M_{52}$  und  $M_{56}$  bilden Weglängenunterschiede auf Grund der unterschiedlichen Position der Teilchen im Strahl ab. Eine Auflistung der Transportmatrizen ist in Anhang B.1 gegeben.

Neben der Beschreibung der externen Kräfte in Form von Matrizen spielen auch die Selbstfelder eines Strahls mit Raumladung eine wichtige Rolle. Dabei gilt es, diese Felder zu berechnen und ihre Auswirkungen auf die Teilchen zu beschreiben. Die Abbildung dieser kollektiven Effekte im Rahmen der Simulation soll im Folgenden skizziert werden.

Um die Berechnungen im Rahmen der Simulation zu reduzieren, kommt zur Beschreibung der Raumladungskräfte, die von den Teilchen ausgehen oder auf diese wirken, ein Gitter zum Einsatz. Statt also den Einfluss jedes Teilchens auf jedes andere Teilchen berechnen zu wollen (sog. n-Body Simulation mit einem Aufwand von  $O(n^2)$ ), werden Felder und Kräfte nur auf den nächstliegenden Gitterpunkten diskretisiert betrachtet. Diese Technik wird Particle-in-cell (PIC) Methode genannt. Die Methode wird bereits seit den 1950er Jahren für Plasmasimulationen eingesetzt [vgl. BL05, S. 3]. Der Begriff Particle-in-cell veranschaulicht, dass sich die einzelnen Teilchen im Rahmen der Simulation in den Gitterzellen aufhalten. Bei sog. 1D-Simulationsprogrammen wird nur der longitudinale Raum betrachtet, bei 2D-Programmen betrachtet man den transversalen Raum und bei 3D-Programmen den vollständigen Raum. Als Mischform existiert auch die sog. 2,5D-PIC-Simulation, hierbei werden die Teilchenkoordinaten in 3D simuliert, für die Berechnung der Felder wird die z-Koordinate in Scheiben zusammengefasst, da es für manche Teilchenverteilungen sehr komplex ist, die Selbstfelder im vollen 3D-Raum zu berechnen.

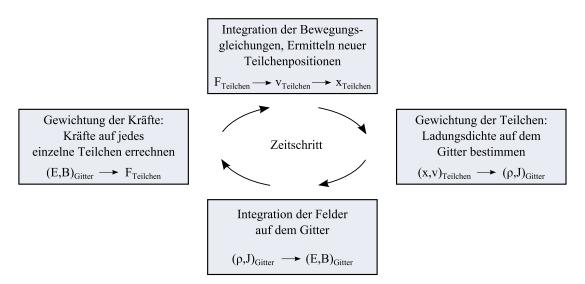

Der Berechnungszyklus eines diskreten Zeitschritts im Rahmen einer PIC-Simulation ist in Abb. 2.2 dargestellt [vgl. BL05]. Der Startpunkt ist eine Teilchenverteilung im

Abbildung 2.2: Berechnungszyklus einer Particle-in-cell Simulation (basierend auf [BL05, Abb. 2-3a]).

Raum. Ausgehend von der Teilchendichte wird im ersten Schritt eine Ladungs-  $(\rho)$  und Stromverteilung (J) auf dem Gitter interpoliert. Daraus wird im zweiten (engl. auch "field solver" bezeichneten) Schritt das elektrische und magnetische Raumladungsfeld auf dem Gitter bestimmt; dies kann z. B. mit Hilfe einer vorwärts- und rückwärts-FFT Funktion durchgeführt werden. Das elektromagnetische Feld wird integriert und ergibt ein elektrostatisches Potential [vgl. Rei08, S. 173]. Im dritten Schritt werden aus dem Potential Kräfte auf die Teilchen bestimmt, die genau wie ablenkende oder beschleunigende Kräfte auf die Teilchen einwirken [vgl. Rei08, S. 164]. Aus diesen Kräften können dann im letzten (engl. auch "particle pusher" bezeichneten) Schritt die neuen Teilchenpositionen ermittelt werden.

Im Rahmen der Simulationen werden Strahlgrößen ermittelt und ihre Veränderung über den Simulationsverlauf beobachtet. Im Vordergrund steht dabei die Strahlqualität (Güte des produzierten Strahls) und die Strahlintensität (Zahl der Teilchen pro Zeiteinheit) [vgl. Hin08, S. 6ff.]. Ein Parameter, der die Strahlqualität beschreibt, ist die rms-Emittanz (root mean square Emittanz,  $1\sigma$ -Abweichung). Sie misst die geometrischen Bündelung des Strahls um die Sollbahn, d. h. Strahlbreite mal Divergenz und ist wie folgt definiert [vgl. Rei08, S. 321] bzw. [vgl. Hin08, S. 171]:

$$\epsilon_x = \sqrt{\langle x^2 \rangle \langle x'^2 \rangle - \langle xx' \rangle^2}$$

(2.1.5)

Analog wird die Emittanz in y-Richtung definiert (angegeben in mm  $\times$  mrad). Angestrebt wird eine möglichst kleine Emittanz. Die Emittanz als Messgröße soll im Folgenden als beispielhafte Messgröße dienen. Ihre Berechnung enthält die typische Anforderung, dass Werte einzelner Teilchen über den gesamten Strahl zusammengefasst werden müssen. Auf die Berechnung weiterer Strahlgrößen wird in dieser Arbeit verzichtet, da sie keine darüber hinausgehenden Anforderungen an die Parallelisierung stellen.

### 2.2 Parallelverarbeitung

Zum Lösen großer Berechnungsprobleme mit Hilfe von Computern konnte man sich in der Vergangenheit darauf verlassen, dass die Berechnungen mit der nächsten Computergeneration um ein Vielfaches schneller durchführbar waren. So symbolisiert Moores Gesetz aus dem Jahr 1965, nach dem sich die Anzahl der Transistoren auf einem Chip alle 18 Monate verdoppelt, den rasanten technologischen Fortschritt der Computerindustrie. In den letzten Jahren wurden allerdings zunehmend Grenzen erreicht, über die hinaus eine weitere Erhöhung von Taktraten, Verkleinerung von Transistoren oder Verkürzung von Signallaufzeiten nicht mehr unbegrenzt möglich erscheint [vgl. Tan05, S. 43f.]. Um dennoch die Leistung aktueller Computer weiter zu steigern, wird in zunehmendem Maße Parallelverarbeitung eingesetzt.

Parallelverarbeitung bedeutet, dass mehrere Aufgaben gleichzeitig durchgeführt werden können. Bezogen auf die Informatik versteht man darunter die gleichzeitige Ausführung unterschiedlicher Aufgaben durch zwei oder mehr Prozessoren, entweder durch einen Rechner mit mehreren zentralen Ausführungseinheiten oder durch mehrere Rechner, die über ein Kommunikationsnetzwerk verbunden sind (übersetzt aus "The American Heritage Dictionary of the English Language" und [vgl. WA04, S. 5]).

Im Folgenden sollen zunächst parallele Rechnerarchitekturen vorgestellt werden. Im Anschluss wird das Modell für Parallelrechner vorgestellt, welches den theoretischen Betrachtungen und Abschätzungen zu Grunde liegt. Danach folgt eine Auflistung wichtiger Messgrößen für parallele Programme. Nach diesen theoretischen Betrachtungen wechselt der Fokus hin zur Parallelen Entwicklung. Es wird zunächst die eingesetzte Methode zum Entwurf paralleler Algorithmen vorgestellt, bevor kurz auf die praktische Implementierung mittels MPI eingegangen wird (dem Thema GPU ist später ein eigenes Kapitel gewidmet, weshalb die GPU hier noch nicht angesprochen wird). Abschließend werden spezielle Techniken und Modelle angesprochen, die im Rahmen der Arbeit eine Rolle spielen.

#### 2.2.1 Parallele Rechnerarchitekturen

Bei der Parallelverarbeitung kann bei genauerer Betrachtung die eigentliche Parallelität in der Ausführung auf unterschiedlichen Ebenen stattfinden: auf Befehlsebene in Form von Pipelining, auf Prozessorebene in Form von Feldrechnern oder Vektorrechnern, auf Ebene des einzelnen Computers in Mehrprozessorsystemen, oder auf der Ebene vieler Computer in Form von lose gekoppelten Multicomputersystemen [vgl. Tan05, S. 80ff.]. Im Folgenden werden die zwei grundlegenden Arten von Parallelrechnern, die Mehrprozessorsysteme und Multicomputersysteme, sowie das zu Grunde liegende Einprozessorsystem näher betrachtet [vgl. WA04, S. 14ff.].

Ein herkömmlicher Rechner ist ein *Einprozessorsystem*. Er basiert auf der Von-Neumann-Architektur aus den 1940er-Jahren bestehend aus einem zentralen Steuerund Rechenwerk, einem Speicher für Programm und Daten und einer Ein- und Ausgabeeinheit. Mit einem solchen System ist keine Parallelverarbeitung möglich. Um dem Benutzer dennoch den Eindruck einer gleichzeigtigen Ausführung mehrerer Aufgaben zu geben, werden diese im Zeitscheibenverfahren nacheinander ausgeführt.

Bei einem *Mehrprozessorsystem mit gemeinsamem Speicher* (engl. shared memory multiprocessor system) werden in einem Rechner mehrere Prozessoren eingesetzt. Alle Prozessoren können auf den gemeinsamen Speicher zugreifen, dieser wird als ein Adressraum zur Verfügung gestellt und beinhaltet Programm und Daten. Je nachdem, ob auf diesen gemeinsamen Speicher von allen Prozessoren gleich schnell zugegriffen werden kann, oder der Zugriff auf entfernte Speicherstellen länger dauert, unterscheidet man dabei die Untertypen UMA und NUMA (engl. für (non) unified memory access). Jeder Prozessor besitzt zusätzlich lokale, schnelle Speicher (sog. Caches) in denen bereits gelesene Daten gehalten werden, um nicht wiederholt auf den gemeinsamen, i. A. langsameren Speicher zugreifen zu müssen. Der Vorteil bei der Programmierung eines solchen Systems liegt darin, dass von jedem Prozessor aus auf alle Daten zugegriffen werden kann. Der Nachteil liegt darin, dass Mechanismen zur Konfliktbehandlung bei gleichzeitigen Zugriffen auf den gemeinsamen Speicher und zur Herstellung von Cache-Kohärenz nötig sind [vgl. WA04, S. 14 ff.].

Bei einem *Multicomputersystem mit verteiltem Speicher* (engl. distributed memory multicomputer system) werden mehrere unabhängige Rechner über ein Verbindungsnetzwerk zusammengeschlossen. Jeder einzelne Rechner kann wiederum ein Ein- oder Mehrprozessorsystem sein, d.h. jeder Rechner des Multicomputersystems hat einen oder mehrere eigene Prozessoren und seinen eigenen lokalen Speicher. Auf den Speicher anderer Rechner kann nicht zugegriffen werden, es handelt sich um sog. verteilten Speicher. Daten werden zwischen den einzelnen Rechnern per Nachrichtenaustausch übertragen. Der Vorteil bei einem Multicomputersystem ist die einfache Skalierbarkeit des Gesamtsystems, es können jederzeit weitere Rechner hinzugefügt werden, der Engpass ist hierbei das Verbindungsnetzwerk. Nachteil ist die kompliziertere Programmierung des Nachrichtenaustauschs. Außerdem müssen Überlegungen zur Einbettung in die bestehende Netzwerktopologie bereits beim Algorithmenentwurf einbezogen werden.

Die beiden oben beschriebenen Arten von Parallelrechnern stellen die beiden klassischen Kategorien dar. Da die Art des Speichers – also gemeinsamer Speicher (shared memory) oder verteilter Speicher (distributed memory) – losgelöst ist von der Rechnerarchitetur selbst, gibt es weitere Mischformen. So kann mit Hilfe einer Softwareabstraktionsschicht auch auf einem Multicomputersystem dem Entwickler gegenüber der Eindruck eines gemeinsamen Speichers vermittelt werden (sog. distributed shared memory), genauso können umgekehrt auf einem Mehrprozessorsystem die einzelnen Prozesse über Nachrichten kommunizieren, ohne auf einem gemeinsamen Speicher aufzusetzen.

Neben einer Beschreibung des Aufbaus als Mehrprozessor- oder Multicomputersystem und einer Einordung nach Art des Speichers als gemeinsamer oder verteilter Speicher können Parallelrechner allgemein nach ihren Befehlsströmen (einer oder mehrere: single/multiple instruction stream) und ihren Datenströmen (einer oder mehrere:

single/multiple data stream) mittels der Klassifikation von Flynn (1966) kategorisiert werden [vgl. Tan05, S. 621]:

- SISD (ein Befehlsstrom, ein Datenstrom): klassischer Einprozessorrechner mit Von-Neumann-Architektur

- SIMD (ein Befehlsstrom, mehrere Datenströme): Feldrechner oder Vektorrechner, die Steuereinheit gibt hierbei einen Befehl vor, der mit einer Menge von Daten gleichzeitig operiert, typischerweise liegen die Daten in Form eines Arrays vor

- MISD (mehrere Befehlsströme, ein Datenstrom): keine Realisierung bekannt

- MIMD (mehrere Befehlsströme, mehrere Datenströme): hierzu zählen die oben beschriebenen Multiprozessor- und Multicomputersysteme

Aufbauend auf der Klassifikation nach Flynn existieren heute weitere Unterklassen auf die speziell im Zusammenhang mit der GPU in Kap. 2.3.5 eingegangen wird.

Im Rahmen dieser Arbeit sind unterschiedliche parallele Architekturen von Interesse. Das Simulationsprogramm PATRIC beinhaltet bereits eine Implementierung für Multicomputersysteme, wobei die einzelnen Knoten per Nachrichtenaustausch kommunizieren. Dieser Aufbau mit mehreren eigenständigen Rechnern gehört zur Kategorie MIMD. Die im Rahmen dieser Arbeit betrachtete GPU kann zunächst als spezialisierter Prozessor, dessen Aufgabe die massiven Berechnungen im Rahmen der Grafikverarbeitung ist, in Analogie zu [Tan05, S. 601, S. 610] als eine Art eigenständiger Koprozessor angesehen werden. Bei näherer Betrachtung der Arbeitsweise der GPU selbst finden sich Parallelen zum Vektorrechner. Die einzelnen Verarbeitungseinheiten auf der GPU fallen in die Kategorie SIMD, da hier ein Programm mit unterschiedlichen Daten parallel ausgeführt werden kann, zum Datenaustausch existiert ein gemeinsamer Speicher. Auf diese zunächst grobe Einordnung wird in den jeweiligen Kapiteln noch näher eingegangen.

### 2.2.2 Modelle für Parallelrechner

Beim Algorithmenentwurf wird von der konkreten Hardware abstrahiert, stattdessen wird als Grundlage ein theoretisches Modell des Rechners verwendet. Diese Vorgehensweise ermöglicht es, Algorithmen zu entwerfen und zu formulieren, die einfach beschreibbar sind, ohne bereits auf die Laufzeitumgebung, vorhandene Programmschnittstellen, usw. Rücksicht nehmen zu müssen. Neben der Unterstützung des Entwurfs soll diese Abstraktion auch eine einfache theoretische Analyse der Algorithmen ermöglichen, die für alle konkreten Implementierungen auf Parallelrechnern Gültigkeit besitzt. Im Vordergrund stehen dabei Aussagen zu Laufzeit, Rechenaufwand, Speicherbedarf und Anzahl benötigter Prozessoren.

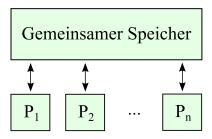

Als theoretisches Modell für Parallelrechner mit gemeinsamem Speicher existiert das Modell der PRAM (Parallel Random Access Machine) [vgl. JáJ92, S. 9ff.], das auf dem Modell der RAM (Random Access Machine) aufsetzt, welche zur Analyse sequentieller Programme verwendet wird [vgl. AHU74, S. 5ff.]. Eine PRAM besteht aus einer

Abbildung 2.3: Modell mit gemeinsamem Speicher (shared-memory), das auch der PRAM zu Grunde liegt (basierend auf [JáJ92, Abb. 1.3]).

Reihe von Prozessoren, die einen synchronen Takt haben. Sie sind unterscheidbar durch einen eindeutigen Index, auf den im Programm zugegriffen werden kann. Jeder Prozessor besitzt einen eignen lokalen Speicher. Daneben existiert ein gemeinsamer globaler Speicher, auf den alle Prozessoren Zugriff haben und über den Daten ausgetauscht werden können, siehe Abb. 2.3. Hier wird der Untertyp der CRCW PRAM (concurrent read, concurrent write) verwendet, der einen gleichzeitigen Zugriff aller Prozessoren auf die Speicherstellen erlaubt. Lesen ist dabei tatsächlich gleichzeitig möglich, ein konkurrierender Schreibzugriff ist entweder nur erlaubt, wenn alle beteiligten Prozessoren denselben Wert schreiben wollen oder führt dazu, dass nur ein Prozessor schreiben darf (zufällig oder prioritätsgesteuert). Die Behandlung eines konkurrierenden Schreibzugriffs ist nicht nur bei der theoretischen Betrachtung nötig, um Schreibkonflikte aufzulösen, sondern muss auch bei der tatsächlichen Programmierung von Parallelrechnern berücksichtigt und mit geeigneten Mitteln gelöst werden.

Die Formulierung von Algorithmen für die PRAM erfolgt in Form von Pseudocode, wobei das Schlüsselwort pardo genutzt wird, um anzuzeigen, dass der folgende Quelltextblock parallel ausgeführt werden soll. Dabei wird die Notation aus [JáJ92] verwendet.

Bei der theoretischen Analyse von Algorithmen interessiert man sich für deren Komplexität in Bezug auf eine bestimmte Problemgröße; hierzu abstrahiert man von einer konkreten Eingabe und betrachtet die Komplexität als die größte Komplexität bei einer gegebenen Eingabelänge [vgl. Akl89, S. 22]. Interessant sind vor allem die Laufzeit und der Aufwand eines parallelen Algorithmus.

Die (parallele) *Laufzeit* kann dabei bestimmt werden durch die maximale Anzahl der Befehle, die einer der parallelen Prozessoren zur Abarbeitung seines Teils benötigt (d. h. vom Beginn der Berechnung bis zum Programmende). Der *Aufwand* ist die Summe aller Befehle, die zur Ausführung des gesamten Algorithmus auf allen beteiligten parallelen Prozessoren nötig sind [vgl. JáJ92, S. 31]. Hierbei sei ein uniformes Kostenmaß zur Ermittlung der Laufzeit einzelner Befehle zu Grunde gelegt, d. h. alle Befehle werden als gleich lang dauernd angesehen [vgl. AHU74, S. 12]. Da man generell an der ungünstigsten Komplexität bei einer bestimmten Eingabelänge interessiert ist (worst-case Analyse), steht eine asymptotische Betrachtung im Vordergrund, bei der konstante Faktoren unterdrückt werden.

Die Einordnung der Algorithmen erfolgt in Klassen, welche mittels der O-Notation angegeben werden (Ordnung). Dabei ist die Laufzeit *T* (bzw. der Aufwand *W*) in Abhängigkeit von der Eingabelänge *n* definiert als [JáJ92, S. 5]:

$$T(n) = O(f(n))$$

wenn es positive Konstanten  $c$  und  $n_0$  gibt, so dass  $T(n) \le c \cdot f(n)$  für alle  $n \ge n_0$  gilt. (2.2.1)

Die O-Notation wird im Folgenden zur Abschätzung der Komplexität von Algorithmen verwendet.

Neben dem beschriebenen PRAM Modell für Parallelrechner existieren weitere Modelle, speziell auch für solche mit Nachrichtenaustausch (z. B. das BSP-Modell, bulk synchronous parallel model [vgl. Val90]), die auch die Kommunikations- und Synchronisationskosten bei verteilten Systemen mit einbeziehen. Trotz der Verwendung von Multicomputersystemen basierend auf verteiltem Speicher und Nachrichtenaustausch in einem Teil der verwendeten Programme liegt der Schwerpunkt dieser Arbeit auf dem Einbezug der lokal vorhandenen GPU. Zur Analyse der Algorithmen auf der GPU wird entsprechend das Modell der PRAM verwendet, siehe auch Kap. 2.3.5.

#### 2.2.3 Maße für Parallelität

Neben der Analyse der Algorithmen auf Basis eines Modells des Parallelrechners spielen Messgrößen bei der Beurteilung der parallelen Algorithmen und Programme eine wichtige Rolle. Mit ihnen soll z. B. gemessen werden, um wieviel schneller das parallele Programm gegenüber dem sequentiellen tatsächlich ist. Im Folgenden werden die wichtigsten Messgrößen vorgestellt. Im praktischen Teil dieser Arbeit finden sie Verwendung bei der Analyse der Programme.

Eine zentrale Messgröße ist die Beschleunigung (engl. speedup), die angibt, um wieviel schneller der vorliegende parallele Algorithmus mit Laufzeit  $t_p$  im Verhältnis zum besten sequentiellen Algorithmus<sup>2</sup> mit Laufzeit  $t_s$  ist [vgl. WA04, S. 6]:

$$S(p) = \frac{t_s}{t_p} \tag{2.2.2}$$

Die Laufzeit kann dabei in der theoretischen Untersuchung der Anzahl der Berechnungsschritte oder Befehle entsprechen (vgl. Kapitel 2.2.2) oder aber bezogen auf ein vorliegendes Programm die gemessene Laufzeit bei dessen Ausführung darstellen.

Die maximale Beschleunigung mit p Prozessoren entspricht bei Betrachtung der Gleichung zunächst p (lineare Beschleunigung). In seltenen Fällen kann z. B. auf Grund größerer Caches in Parallelrechnern eine superlineare Beschleunigung (S(p) > p) auftreten [vgl. WA04, S. 7]. Im Allgemeinen ist die Beschleunigung jedoch kleiner als

<sup>&</sup>lt;sup>2</sup>Es sei generell angemerkt, dass bei Messungen im praktischen Teil der Arbeit als "bester sequentieller Algorithmus" immer das jeweils gegebene sequentielle Programm angenommen wird.

die Zahl der im parallelen Fall eingesetzten Prozessoren ( $S(p) \le p$ ). Dies ist bedingt dadurch, dass im parallelen Algorithmus weiterer Aufwand anfällt, z. B. durch zusätzliche lokale Berechnungen, Kommunikationsaufwand zwischen den Prozessoren oder einfach der Tatsache, dass die vorhandene Arbeit nicht gleichmäßig aufgeteilt werden kann und deshalb einzelne Prozessoren teilweise unbeschäftigt sind [vgl. WA04, S.8] und [vgl. Sch00, S.42].

Zur Frage nach der maximal erreichbaren Beschleunigung eines Algorithmus existieren zwei sehr unterschiedliche Ansätze. Amdahls Gesetz (1967) beantwortet die Frage bezogen auf den parallelisierbaren Anteil des Algorithmus. Der Algorithmus besteht demnach aus einem seriellen Teil f, der nicht parallelisiert werden kann und einem Teil (1-f), bei dem dies möglich ist. Ausgegangen wird hier von einer fixen Problemgröße und von keinem zusätzlichen Aufwand durch die Parallelisierung. Entsprechend ist hiernach die Beschleunigung auch definierbar als [vgl. WA04, S. 8]:

$$S(p) = \frac{t_s}{f \cdot t_s + \frac{(1-f) \cdot t_s}{p}} = \frac{p}{1 + (p-1)f} \quad \text{mit} \quad \lim_{p \to \infty} S(p) = \frac{1}{f}$$

(2.2.3)

Nach Amdahls Gesetz hängt also die maximal mögliche Beschleunigung fest vom parallelisierbaren Anteil des Algorithmus ab, egal wie viele Prozessoren eingesetzt werden. Diese Betrachtungsweise der Möglichkeiten der Parallelisierung wird als zu pessimistisch angesehen [vgl. Sch00, S.43]. Nichtsdestotrotz spielt sie dennoch eine wichtige Rolle beim Algorithmenentwurf. Sie macht deutlich, dass der paralleliserbare Anteil eines Algorithmus so groß wie möglich gestaltet werden sollte, um eine hohe Beschleunigung zu erreichen.

Gustafson (1988) vertritt demgegenüber einen anderen Ansatz bei der Bestimmung der maximal erreichbaren Beschleunigung. Dieser geht davon aus, dass der serielle Teil des Problems statisch ist und somit insb. nicht größer wird, wenn man die Problemgröße erhöht. Bei diesem Ansatz wird von einer festen Zeit ausgegangen, die der Algorithmus benötigen soll; eine Erhöhung der Anzahl der eingesetzten Prozessoren führt hierbei zu der Möglichkeit, ein größeres Problem bearbeiten zu können. Die Definition der Beschleunigung und die maximale Beschleunigung ergeben sich hiernach zu [vgl. WA04, S. 12]:

$$S(p) = \frac{f \cdot t_s + (1 - f) \cdot t_s}{f \cdot t_s + \frac{(1 - f) \cdot t_s}{p}} = p + (1 - p) \cdot f \cdot t_s \qquad \text{mit} \qquad \lim_{p \to \infty} S(p) = p$$

(2.2.4)

Der parallele Anteil wächst also, je mehr Prozessoren eingesetzt werden.

Beide Ansätze haben in der parallelen Entwicklung ihre Berechtigung. In der Realität wird die maximal erreichbare Beschleunigung zwischen diesen beiden Extrembetrachtungen liegen, da der nicht parallelisierbare Anteil typischerweise mit dem Einsatz einer größeren Anzahl an Prozessoren zwar geringer wird, aber wie oben angedeutet weiterer Aufwand für die Parallelverarbeitung hinzukommt. Beide Ansätze müssen demnach bei der Entwicklung paralleler Algorithmen berücksichtigt werden, zeigen sie doch deutlich die Grenzen der Parallelisierbarkeit auf.

Eine weitere Messgröße für parallele Algorithmen ist die *Effizienz*, die angibt, wie lang im Schnitt die einzelnen Prozessoren an der Berechnung beteiligt sind, d.h. ob im parallelen Fall alle Prozessoren ausgelastet sind.

$$E = \frac{t_s}{t_p \cdot p} \tag{2.2.5}$$

Bei Algorithmen für Multicomputersysteme spielt zusätzlich die Kommunikationszeit eine bedeutende Rolle. Messgrößen in diesem Zusammenhang sind die Latenz (Zeitspanne vom Senden des Pakets bis zur Antwort) und Bandbreite (welche Datenmenge das System pro Zeiteinheit übertragen kann) [vgl. Tan05, S. 676]. Speziell für die Abschätzung, wie groß die einzelnen Anteile an der Gesamtberechnung sein sollen, die einzelne Berechnungsknoten bearbeiten, ist das Verhältnis von eigentlicher Berechnungszeit  $t_{comp}$  zu Kommunikationszeit  $t_{comm}$  von Bedeutung:

Rechenzeit zu Kommunikationszeit =

$$\frac{t_{comp}}{t_{comm}}$$

(2.2.6)

Hierbei muss eine gute Balance gefunden werden zwischen der Möglichkeit zur parallelen Berechnung einerseits und der mit zunehmender Parallelisierung steigender Kommunikation andererseits.

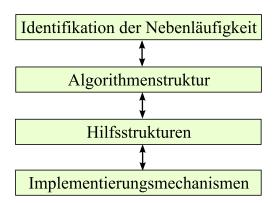

### 2.2.4 Entwurf paralleler Algorithmen

Der Schlüssel zur Parallelverarbeitung ist das Existieren von "ausnutzbarer" Parallelität [vgl. MSM05, S. 3]. D. h. ein gegebenes Problem muss nebenläufige Teilprobleme enthalten, aber auch in einer Art und Weise formulierbar sein, dass diese Teilprobleme tatsächlich parallel abgearbeitet werden können. Das Ziel ist ein paralleler Algorithmus, d. h. eine Lösungsmethode für ein gegebenes Problem, die dafür ausgelegt ist, auf einem Parallelrechner ausgeführt zu werden [vgl. Akl89, S. 3]. Aus diesem Grund ist die Aufgabe des Entwicklers bei dem Entwurf paralleler Algorithmen, die Nebenläufigkeit in dem gegebenen Problem zu entdecken und den Algorithmus entsprechend zu strukturieren. Danach folgt die Implementierung in einer passenden Programmierumgebung, bevor das Programm dann in einer parallelen Laufzeitumgebung ausgeführt werden kann [vgl. MSM05, S. 3]. Der Schlüssel steckt also im Entwurf der Algorithmen, speziell im Erkennen und Formulieren der parallelen Aspekte.

Eine standardisierte Methode zum Entwurf paralleler Algorithmen und der Umsetzung in parallele Programme mit Hilfe von Vorgehensmustern ist in [MSM05] beschrieben. Die Tätigkeiten gliedern sich dabei in verschiedene Schritte, siehe Abb. 2.4. Die Methodik soll im Folgenden kurz vorgestellt werden mit einem Fokus auf den Aspekten, die im Rahmen der Arbeit zum Einsatz kamen. Die Ausführungen folgen dabei [MSM05].

Abbildung 2.4: Vier Schritte beim Entwurf paralleler Algorithmen (basierend auf [MSM05, Abb. 1-1]).

#### 2.2.4.1 Identifikation der Nebenläufigkeit

Bei der Identifikation der Nebenläufigkeit wird zunächst das gegebene Realweltproblem analysiert und es werden parallelisierbare Teile identifiziert. Das Problem wird so strukturiert, dass die Nebenläufigkeit sichtbar und nutzbar gemacht wird. Dies geschieht, indem das Problem zunächst in Teilprobleme zerlegt wird. Als Muster stehen hier entweder die Funktions- oder die Datenzerlegung zur Verfügung.

- Funktionszerlegung: Bei der Funktionszerlegung werden die zur Problemabarbeitung nötigen Schritte betrachtet. Mehrere zusammengehörende Schritte werden zu Funktionen zusammengefasst, die parallel zueinander ausgeführt werden können. Erst als zweites wird überlegt, mit welchen Daten die Funktionen operieren sollen. Diese Zerlegung wird gewählt, wenn die einzelnen Funktionen relativ unabhängig voneinander sind.

- Datenzerlegung: Bei der Datenzerlegung liegt der Fokus auf den Daten und wie diese in geeignete Blöcke zerlegt werden können, die dann parallel bearbeitet werden können. Erst in einem zweiten Schritt wird überlegt, welche Funktionen zur Bearbeitung der Daten nötig sind. Diese Zerlegung wird gewählt, wenn die einzelnen Datenblöcke relativ unabhängig voneinander sind.

Welche Zerlegung gewählt wird, ist nicht immer klar vorgegeben, meist finden beide Aspekte Berücksichtigung, jedoch wird in der Vorgehensweise empfohlen, einer der beiden Zerlegungen den Vorrang zu geben [vgl. MSM05, S. 29].

Da Teilchensimulationen meist aus klar abgegrenzten Einzelschritten bestehen, spielt hierbei vor allem die Funktionszerlegung eine wichtige Rolle. Mit der Überlegung, welche Daten für diese Funktionen benötigt werden, ergibt sich im zweiten Schritt daraus eine geeignete Datenzerlegung (vergleiche auch das Beispiel in [MSM05, S. 29]). Bei speziellen Konfigurationen zur Laufzeit, z. B. in einer verteilten Umgebung mit mehreren Rechenknoten, kann wiederum die Datenzerlegung Verwendung finden. Speziell bei der Datenzerlegung sollten die einzelnen Datenblöcke nicht zu klein werden, damit der Aufwand ihrer Verwaltung nicht zu groß wird [vgl. MSM05, S. 36].

Nachdem das Problem mit Hilfe der Funktions- oder Datenzerlegung in Teilprobleme zerlegt ist, müssen die Abhängigkeiten zwischen diesen Teilproblemen ermittelt werden, um zu entscheiden, welche davon später parallel bearbeitet werden können. Bei der beschriebenen Vorgehensweise werden die Teilprobleme zunächst in solche gruppiert, die gleiche Abhängigkeiten besitzen. Diese Gruppen werden dann entsprechend ihrer Abhängigkeiten in eine zeitliche Abfolge gebracht. In einem nächsten Schritt wird ermittelt, auf welche gemeinsamen Daten die Teilproblemgruppen zugreifen müssen und wie der Zugriff auf diese Daten erfolgen muss.

Eine abschließende Analyse überprüft die gefundene Aufteilung auch im Hinblick auf die gleichmäßige Verteilung der Arbeit. Außerdem wird zum ersten mal in Bezug auf die Zielplattform die Frage beantwortet, ob z.B. für die gefundene Zerlegung genügend Ausführungseinheiten zur Verfügung stehen und ob es Datenstrukturen gibt, um die gemeinsamen Daten verwalten zu können [vgl. MSM05, S. 51].

#### 2.2.4.2 Algorithmenstruktur

Basierend auf dem vorliegenden, in parallel ausführbare Teile zerlegten Realweltproblem folgt im nächsten Schritt der Algorithmenentwurf. Da Programme einen längeren Lebenszyklus besitzen als die Rechner auf denen sie laufen, sollte der Algorithmenentwurf zunächst frei von der Zielplattform erfolgen. Als Randbedingungen in Bezug auf die aktuelle Zielplattform sollten lediglich die Größenordnung der Anzahl der Ausführungseinheiten sowie die Kosten einer Kommunikation zwischen den verschiedenen Ausführungseinheiten einbezogen werden, um einen Algorithmus zu finden, der sich leicht auf der Zielplattform umsetzen lässt [vgl. MSM05, S. 59]. Das Ziel ist ein Algorithmus, der die gefundene Problemzerlegung auf Ausführungseinheiten abbildet.

Je nach Hauptordnungskriterium werden verschiedene Algorithmenstrukturen vorgeschlagen [vgl. MSM05, S. 61]:

- Organisation der Funktionen als Hauptordnungskriterium: für eine lineare Organisation der Funktionsparallelismus (Task Parallelism), für eine rekursive das Muster Teile-und-Herrsche (Divide and Conquer)

- Organisation nach der Datenzerlegung als Hauptordnungskriterium: für eine lineare Datenzerlegung das Muster der geometrischen Zerlegung, für eine rekursive Struktur eine weitere rekursive Datenzerlegung

- Organisation nach der Ordnung der Funktionen und dem damit einhergehenden Datenfluss: bei regulärem Datenfluss das Muster der Pipeline, bei irregulärem Datenfluss eine Koordination mit Hilfe von Nachrichten

Speziell von Interesse bei der Teilchensimulation sind die Algorithmenstrukturen des Funktionsparallelismus und der geometrischen Aufteilung der Daten.

Beim Funktionsparallelismus stehen Fragen nach der Abbildung der Funktionen im Rahmen des Algorithmus, deren Zuordnung zu Ausführungseinheiten, die Berücksichtigung von Abhängigkeiten zwischen den Funktionen und damit die übergreifende Ablaufplanung im Vordergrund [vgl. MSM05, S. 65]. Wichtig ist hierbei, dass es mindestens so viele Funktionen wie Ausführungseinheiten geben sollte (im Idealfall wesentlich mehr, um eine größere Flexibilität bei der Ablaufsteuerung zu erreichen). Die Berechnungen im Rahmen einer Funktion sollten zudem aufwändig genug sein, um den Aufwand zur Verwaltung der Funktionen und der Behandlung der Abhängigkeiten zu rechtfertigen.

Die geometrische Aufteilung der Daten wird immer dann eingesetzt, wenn das zentrale Organisationskriterium beinhaltet, dass zentrale Datenstrukturen in lineare Datenblöcke aufgeteilt werden, auf denen Teillösungen ermittelt werden. Für die Bearbeitung des Problems für die einzelnen Datenblöcke sind dabei typischerweise Daten von wenigen anderen Datenblöcken nötig. Dahinter steckt ein grobgranularer Datenparallelismus basierend auf den Datenblöcken [vgl. MSM05, S. 79].

#### 2.2.4.3 Hilfsstrukturen

Erster Schritt bei der Umsetzung des entworfenen Algorithmus in ein Programm ist die Festlegung auf allgemeine Programmkonstrukte und Strukturen, die es ermöglichen, den parallelen Algorithmus auszudrücken. Dies erfolgt unabhängig von der konkreten Implementierung, dennoch sollten Strukturen gewählt werden, die in der verwendeten Entwicklungsumgebung generell unterstützt werden [vgl. MSM05, S. 119]. Im Fokus stehen hierbei die Programmstrukturen und die Datenstrukturen.

Bei den Programmstrukturen für die Teilchensimulation von Interesse sind vor allem SPMD (single program, multiple data) [vgl. MSM05, S. 128] und der Schleifenparallelismus [vgl. MSM05, S. 152]. Bei SPMD führen verschiedene Ausführungseinheiten dasselbe Programm mit verschiedenen Daten aus. Die einzelnen Knoten sind über eine eindeutige Nummer identifiziert und so kann der Programmablauf von Knoten zu Knoten variieren. Dies ist typisch für verschiedene MPI-Knoten in Systemen mit verteiltem Speicher. Beim Schleifenparallelismus wird nicht das gesamte Programm parallel abgearbeitet, sondern nur einzelne Schleifen, dabei werden voneinander unabhängige Schleifendurchläufe parallel abgearbeitet. Dieses Muster kommt typischerweise zum Einsatz, wenn nur Teile eines bestehenden Programms parallelisiert werden sollen und ermöglicht eine einfache Art der schrittweisen Parallelisierung. (Andere vorgeschlagene Programmstrukturen spielen im Rahmen dieser Arbeit keine besondere Rolle).

Bei den Datenstrukturen spielen bei der Teilchensimulation vor allem die gemeinsam genutzten Daten [vgl. MSM05, S. 174] und speziell die verteilten Arrays [vgl. MSM05, S. 199] eine Rolle. Neben der Einhaltung einer Zugriffsreihenfolge und Synchronisierungsmechanismen bei gleichzeitigem Zugriff auf die Daten muss hierbei speziell darauf geachtet werden, dass die Daten passend zum Ablauf der Berechnung verteilt werden und insb. dort zur Verfügung stehen, wo sie als nächstes für eine Berechnung benötigt werden. (Andere vorgeschlagene Datenstrukturen z. B. gemeinsam genutze Warteschlangen spielen im Rahmen dieser Arbeit keine Rolle).

### 2.2.4.4 Implementierungsmechanismen

Im letzten Schritt liegt der Fokus auf im Rahmen der Parallelen Programmierung typsichen Implementierungsmechanismen, für die es in den meisten parallelen Entwicklungsumgebungen bereits eine entsprechende Unterstützung gibt. Spezielles Augenmerk wird hierbei auf die Verwaltung der parallel auszuführenden Teilaufgaben (z. B. mittels Prozessen und Threads), auf die Synchronisation (Erzwingen der benötigten Abarbeitungsreihenfolge) und die Kommunikation gelegt [vgl. MSM05, S. 216]. Diese Aspekte müssen vor dem Hintergrund der zur Verfügung stehenden Entwicklungsund Laufzeitumgebung bei der Realisierung des Programms beachtet werden.

Obwohl im Rahmen dieser Arbeit auf bestehenden Programmen aufgesetzt wurde und so die grundlegenden Algorithmen bereits vorgegeben waren, wurde die vorgestellte Vorgehensweise zum Entwurf paralleler Algorithmen dennoch bei den Aspekten berücksichtigt, die zu parallelisieren waren. Im praktischen Teil wird jeweils die Art der gewählten Strukturierung angesprochen.

## 2.2.5 Parallele Softwareentwicklung

Zu jedem der in Kap. 2.2.1 vorgestellten parallelen Architekturen gibt es in der Softwareentwicklung eine entsprechende Unterstützung. Da im Rahmen dieser Arbeit die Einbeziehung der GPU im Vordergrund stand, auf welche in Kap. 2.3 näher eingegangen wird, soll an dieser Stelle kurz die Programmierung von Multicomputersystemen mittels Nachrichten-basierter Kommunikation (message-passing) dargestellt werden.

#### 2.2.5.1 Programmierung von Multicomputersystemen mittels MPI

Das Modell der Nachrichten-basierten Kommunikation besteht aus mehreren Prozessen, die jeweils einen lokalen Speicher mit eigenem Adressraum besitzen und die untereinander Nachrichten austauschen können [vgl. GLS99, S. 14]. Ein Datentransfer zwischen den Prozessen bedingt immer Operationen zum Nachrichtenaustausch, die von allen an der Kommunikation beteiligten Prozessen ausgeführt werden müssen [vgl. GLS99, S. 5]. Das zu Grunde liegende Kommunikationsnetzwerk und dessen Aufbau ist nicht Teil des Modells, eine genauere Kenntnis darüber muss aber ggf. beim Algorithmenentwurf einbezogen werden.

MPI (message passing interface) ist eine spezielle Realisierung des Message Passing Modells in Form der Spezifikation einer Bibliothek [vgl. GLS99, S. 13]. Die erste Version des Standards wurde 1994 vom MPI Forum herausgegeben, die aktuelle Version des Standards ist die Version 3.0 vom September 2012 [Mes12]. Durch die Standardisierung von Funktionsnamen, Aufrufsequenzen und Rückgabewerten soll gewährleistet werden, dass die Funktionalitäten der unterschiedlichen MPI-Implementierungen über Programmiersprachen hinweg gleich heissen und sich gleich verhalten. Ein wichtiges Anliegen des Standards ist die Portabilität der Programme.

Speziell für den Nachrichtenaustausch existieren verschiedene Möglichkeiten, so kann dieser blockierend oder nicht-blockierend und gepuffert oder ungepuffert stattfinden. Neben einem einfachen Nachrichtenaustausch über MPI\_Send und MPI\_Recv gibt es eine Reihe kollektiver Kommunikationsmöglichkeiten, zum einen für den Datenaustausch (z.B. mittels MPI\_Bcast, MPI\_Scatter, MPI\_Gather, MPI\_Alltoall) und zum anderen für kollektive Berechnungen (mittels MPI\_Reduce mit den Möglichkeiten für Maximum, Minimum, Summe, Produkt, sowie logischen oder bitweisen Verknüpfungen) [vgl. GLS99, S. 18f.]. Als wichtige Möglichkeit zur Synchronisation der einzelnen Prozesse mittels einer Barriere steht der Befehl MPI\_Barrier zur Verfügung. Für eine vollständige Liste sei auf den Standard verwiesen [Mes12].

Für den MPI-Standard sind eine Reihe sowohl kommerzieller als auch freier Implementierungen verfügbar. Im Rahmen des bestehenden Programms PATRIC wird die freie Implementierung MPICH eingesetzt, welche vom Argonne National Laboratory, verschiedenen Universitäten und weiteren Partnern entwickelt wird. Diese Implementierung existiert für eine Reihe von Architekturen und Betriebssystemen, im Rahmen der Simulationsrechnungen an der GSI kommt sie auf einem Linux-Cluster zum Einsatz. Weiterführende Informationen zu MPICH finden sich in [MPI12].

#### 2.2.5.2 Master-Slave-Modell

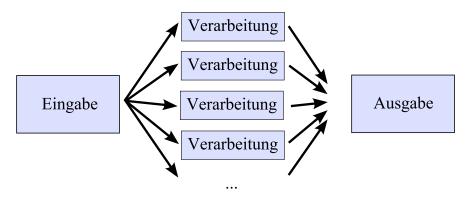

Im Rahmen der Parallelisierung einer Datenverarbeitung wird beim EVA-Prinzip (Eingabe – Verarbeitung – Ausgabe) typischerweise nur der Verarbeitungsschritt mit Hilfe vieler Ausführungseinheiten parallelisiert, wie in Abbildung 2.5 dargestellt [vgl. WA04, S. 80]. Voraussetzung für eine Datenparallelisierung im Allgemeinen ist, dass die Daten unabhängig voneinander verarbeitet werden können. Dies bezieht sich also ebenfalls auf den Verarbeitungsschritt. In der Praxis lässt sich meist die Ein- und Ausgabe nicht parallelisieren, d. h. es besteht der Bedarf, die Daten am Anfang initial aus einer Datenquelle zu lesen und auf die parallelen Ausführungseinheiten zu verteilen und zwischendurch oder am Ende der Berechnung die Ergebnisse wieder zentral zu sammeln und auszugeben.

Um dies zu unterstützen, ist ein gängiges Organisationsprinzip das sog. Master-Slave-Modell [vgl. WA04, S. 79f.]. Hierbei übernimmt ein Prozess (der sog. Master) die zentrale Aufgabe, den anderen Prozessen (den sog. Slaves) Berechnungsaufgaben zuzuteilen und den Ablauf zu steuern. Dieses Prinzip wird insbesondere dann angewendet, wenn die zu verteilenden Aufgaben voneinander unabhängig sind und wenn die Dauer der einzelnen Berechnungen schwer vorherzusagen ist [vgl. GLS99, S. 35]. Ersteres ist gerade bei der Datenparallelisierung gegeben, letzteres ist allein dadurch begründet, dass in der Praxis typischerweise die einzelnen Ausführungseinheiten je nach eingesetzter Hardware und aktueller Auslastung ein unterschiedliches Zeitverhalten zeigen. Eine zentrale Fragestellung beim Master-Slave-Modell ist, wie eine Ausbalancierung (Load-Balancing) zwischen den Slaves erreicht werden kann [vgl. WA04, S. 80].

Das Master-Slave-Modell kann im Rahmen der verteilten Berechnung mittels Nachrichten-basierter Kommunikation realisiert werden. Das Verteilen von Einga-

Abbildung 2.5: EVA-Prinzip vor dem Hintergrund der Parallelverarbeitung.

bedaten und das Einsammeln der Ergebnisse bei Verwendung von MPI kann dabei mit Hilfe der einfachen Funktionen MPI\_Send und MPI\_Recv zum Versenden und Empfangen der Daten oder mit den speziell für diesen Anwendugngsfall angepassten Funktionen MPI\_Scatter (verteilen an mehrere) und MPI\_Gather (Einsammeln der Ergebnisse) bzw. MPI\_Reduce (Verarbeiten beim Einsammeln, z. B. Summenbildung) umgesetzt werden. Beispiele für die Realisierung des Master-Slave-Prinzips mit MPI gibt [GLS99]. Zum Verteilen der Berechnungsaufgaben findet das Master-Slave-Modell mittels MPI bereits Anwendung im bestehenden Simulationsprogramm PATRIC. Hierbei werden die einzelnen Teilstücke eines Teilchenpakets auf die unterschiedlichen MPI-Knoten verteilt, auf denen dann eine lokale Verarbeitung stattfindet. Auf diesen Punkt wird im Rahmen der Beschreibung der Simulationsprogramme näher eingegangen.

Das Master-Slave-Prinzip findet aber auch bei der Grafikkartenprogrammierung Anwendung: der Host kann als Master angesehen werden, der die Daten bereitstellt und die Berechnung steuert. Die parallelen Ausführungseinheiten der Grafikkarte können als Slaves angesehen werden, die die Berechnungen durchführen. Dass die Slaves hierbei voneinander unabhängig arbeiten können, ist jedoch nicht immer gegeben. So kann eine Berechnung auf der Grafikkarte es erfordern, dass sich alle Ausführungseinheiten Synchronisieren, oder sogar zur Ermittlung eines Gesamtergebnisses miteinander interagieren müssen.

# 2.3 Parallelität mit Hilfe von Grafikprozessoren

Da Grafikprozessoren dafür ausgelegt sind, eine Aufgabe (z. B. die Berechnung von Pixelfarben) massiv-parallel mit vielen verschiedenen Eingangsdaten abzuarbeiten (sog. Datenparallelismus), sind sie für die Parallelverarbeitung von großem Interesse. Sie versprechen die Möglichkeit paralleler Abarbeitung, ohne weitere Prozessoren oder gar weitere vernetzte Rechner zu benötigen. Entsprechend werden Grafikprozessoren im Bereich der Supercomputer immer häufiger eingesetzt. So sind nach der aktuellen Veröffentlichung der Top 500 Supercomputersysteme bereits 62 davon mit grafischen Koprozessoren ausgestattet, Tendenz steigend [vgl. TOP12].