# DECstation 5000 Model 240 Workstation Technical Overview

## digital<sup>™</sup>

Worksystems Base Product Marketing Digital Equipment Corporation Palo Alto, California

Version 1.0 December, 1991 Digital believes the information in this publication is accurate as of its publication date; such information is subject to change without notice. Digital is not responsible for any errors in the information given in this publication.

The software described in this document is furnished under license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

The following are trademarks of Digital Equipment Corporation: DEC, DECstation, DEC Ada, DEC FUSE, DEC GKS, DEC PHIGS, DEC VUIT, DECnet, DECwindows, DECsystem, the DIGITAL Logo, PATHWORKS, PixelStamp, TURBOchannel, ULTRIX, VAX, VAXstation, VMS, and XUI.

PostScript is a registered trademark of Adobe Systems, Inc. AT&T and System V are registered trademarks of American Telephone and Telegraph Company. Apple and Macintosh are registered trademarks of Apple Computer, Inc. Network Computing System is a trademark of Hewlett-Packard Company. Intel is a trademark of Intel Corporation. IBM and OS/2 are registered trademarks of International Business Machines Corporation. Lotus is a registered trademark of Lotus Development Corporation. MIPS is a registered trademark of MIPS Computer Systems, Inc. MS-DOS is a registered trademark of Microsoft Corporation. NFS is a trademark of Sun Microsystems, Inc. Open Software Foundation is a trademark and OSF, OSF/1, OSF/Motif, and Motif are registered trademarks of Open Software Foundation, Inc. Open Desktop and SCO are registered trademarks of The Santa Cruz Operation, Inc. UNIX is a registered trademark of UNIX System Laboratories, Inc. X/Open is a trademark of X/Open Company, Ltd.

Copyright © 1991 by Digital Equipment Corporation.

All Rights Reserved.

Printed in U.S.A.

## **Table of Contents**

| 1 | Intro                                              | oduction                          |                                                                                                                                               | 1      |

|---|----------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2 | System Description                                 |                                   |                                                                                                                                               |        |

|   | 2.1                                                | Enclos                            | sure and Environmental Requirements                                                                                                           | 3      |

|   | 2.2                                                | CPU Subsystem                     |                                                                                                                                               | 3      |

|   |                                                    | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4  | The RISC Philosophy<br>The MIPS R3000A RISC Architecture<br>The DS5000/240 CPU Subsystem<br>Cache Architecture, Implementation, and Operation | 6<br>7 |

|   | 2.3                                                | Syster                            | n Memory                                                                                                                                      | 9      |

|   | 2.4                                                | 2.4 TURBOchannel I/O Interconnect |                                                                                                                                               |        |

|   | 2.5                                                | I/O Su                            | bsystem                                                                                                                                       | . 12   |

|   |                                                    | 2.5.1<br>2.5.2<br>2.5.3           | Serial Ports<br>SCSI Interface<br>Ethernet Interface                                                                                          | . 12   |

|   | 2.6                                                | TURB                              | Ochannel Options                                                                                                                              | . 13   |

|   | 2.7                                                | CPU F                             | Performance Measurement                                                                                                                       | . 14   |

| 3 | Syst                                               | em Soft                           | ware                                                                                                                                          | . 17   |

|   | 3.1                                                | ULTRI                             | X Operating System                                                                                                                            | . 17   |

|   | 3.2 Software Development Environment and Compilers |                                   |                                                                                                                                               | . 18   |

|   |                                                    | 3.2.1<br>3.2.2<br>3.2.3           | Languages and Compiler Technology<br>DEC C++ and Object-oriented Software Development<br>DEC FUSE                                             | . 19   |

|   | 3.3                                                | DECw                              | indows and Graphical User Interfaces                                                                                                          | . 21   |

|   |                                                    | 3.3.1<br>3.3.2<br>3.3.3           | DECwindows<br>OSF/Motif and VUIT<br>Extensions to the X Protocol: PEX, Display PostScript, and Xv                                             | . 23   |

|   | 3.4                                                |                                   | ics Programming Interfaces                                                                                                                    |        |

|   |       | 3.4.1   | Display PostScript                                  | 25 |

|---|-------|---------|-----------------------------------------------------|----|

|   |       | 3.4.2   | DEC PHIGS and PEXIib                                | 26 |

|   |       | 3.4.3   | GKS and GKS-3D                                      | 27 |

|   | 3.5   | Networ  | king Software                                       | 27 |

|   |       | 3.5.1   | TCP/IP                                              | 27 |

|   |       | 3.5.2   | Network File System                                 | 28 |

|   |       | 3.5.3   | DECnet/OSI                                          | 28 |

|   |       | 3.5.4   | Network Application Support                         | 28 |

|   | 3.6   | Applica | tion Software                                       | 29 |

| 4 | Grap  | hics Op | tions                                               | 31 |

|   | 4.1   | Graphi  | cs Options Overview                                 | 31 |

|   | 4.2   | MX Gra  | aphics Option                                       | 34 |

|   | 4.3   | TX Gra  | phics Option                                        | 34 |

|   | 4.4   | HX Gra  | aphics Option                                       | 34 |

|   | 4.5   | Accele  | rated 3D Graphics Options                           | 35 |

|   |       | 4.5.1   | The Rendering Pipeline in the DECstation 3D Options | 36 |

|   |       | 4.5.2   | PXG, PXG+, and PXG Turbo+ Options                   | 38 |

|   | 4.6   | Graphi  | cs Performance Characteristics                      | 39 |

|   |       | 4.6.1   | Peak Performance Measurements                       | 39 |

|   |       | 4.6.2   | Picture Level Benchmark Results                     | 41 |

|   | 4.7   | Multisc | reen Support                                        | 42 |

| 5 | Multi | media O | ptions                                              | 43 |

|   | 5.1   | DECm    | edia Hardware Options                               | 44 |

|   |       | 5.1.1   | DECvideo/PIP Option                                 | 44 |

|   |       | 5.1.2   | DECaudio Hardware Option                            | 44 |

|   |       | 5.1.3   | Multimedia Memory, Storage, and CD-ROM              | 45 |

|   | 5.2   | Multime | edia Software                                       | 45 |

|   |       | 5.2.1   | XMedia Tools Video Software                         | 46 |

|   |       | 5.2.2   | XMedia Tools Audio Software                         | 47 |

|   |       | 5.2.3   | Software Motion Pictures                            | 48 |

| 5.2.4 | DECstation FAXserver       | 48 |

|-------|----------------------------|----|

| 5.2.5 | Desktop Video Conferencing | 48 |

## List of Figures

| Figure 2.1 | DECstation 5000/240 System Block Diagram | 4  |

|------------|------------------------------------------|----|

| Figure 3.1 | Compiler Architecture                    | 19 |

| Figure 3.2 | X Window System Architecture             | 23 |

| Figure 3.3 | Graphics Programming System Architecture | 25 |

| Figure 3.4 | NAS Architecture                         | 28 |

| Figure 4.1 | Generic Raster Graphics System           | 32 |

| Figure 4.2 | Graphics Acceleration Architecture       | 35 |

## List of Tables

| Table 4.1 | <b>Graphics</b> Options | Summary |  | 31 |

|-----------|-------------------------|---------|--|----|

|-----------|-------------------------|---------|--|----|

## **1** Introduction

The DECstation 5000/240 workstation is the new high-performance flagship of Digital's RISCbased desktop workstation family. Specifically and briefly, the DECstation 5000/240<sup>1</sup> workstation's CPU measured system performance is rated at 42.9 MIPS, 32.4 SPECmarks, and 10.8 MFLOPS (see Section 2.7 for discussion of performance measurement details). This processing power and commensurate I/O performance make the DS5000/240 suitable for a broad range of compute-intensive applications in science, medicine, geophysics, engineering, economics, and business. Equipped with appropriate selections from the wide range of available graphics options and other I/O peripherals, the DS5000/240 is well suited for work in mechanical CAD/CAM, molecular modeling, electronics design automation, data visualization, image processing, laboratory data acquisition, animation and multimedia presentations, technical publishing, and software development.

The improvements in performance and in price/performance of the DS5000/240 result from the use of faster processors, but also from substantially higher levels of circuit integration. The faster CPU is the 40 MHz R3400 version of the MIPS<sup>®</sup> R3000A architecture, which is itself more highly integrated because it now contains the floating point acceleration in the same VLSI package. In addition, the DS5000/240 features four new Application Specific Integrated Circuits (ASICs) developed by Digital, which together replace more than a hundred of the discrete integrated circuits used in the DS5000/240's predecessor, the DECstation 5000/200. Higher reliability is another important benefit of the higher degree of integration.

Of course, the DS5000/240 remains binary compatible with all of Digital's RISC-based workstations: the DECstation 5000 Models 20, 25, 120, 125, 133, and 200, as well as the DECstations 2100 and 3100. It is also source compatible with applications written for VAX/ULTRIX workstations.

Like all the DECstation 5000 models, the DS5000/240 workstation's I/O is based on the TURBOchannel open interconnect developed by Digital and now the designated highbandwidth interconnect in the Advanced RISC Computer specification (ARC) of the Advanced Computing Environment (ACE) initiative. An improved I/O controller ASIC provides integral interfaces for SCSI devices, Ethernet, serial devices and communications, and a realtime clock. In addition, the DS5000/240 system provides three TURBOchannel option slots for connecting optional peripherals available both from Digital and from third-party suppliers.

<sup>&</sup>lt;sup>1</sup> The term DS5000/240 will be used throughout this overview to refer to the DECstation 5000/240 workstation, unless otherwise noted.

Along with the DECstation 5000/240, Digital is introducing several new TURBOchannel-based graphics options and multimedia options. These new options are not specific to the DS5000/240, but can be used with the other models of the DECstation 5000 family as well. Two of these new graphics options are based on the architectures of previous graphics options, but use faster integrated circuits. Two of the new graphics options implement entirely new architectures, one intended in particular to support the multimedia options.

From its inception, the DECstation 5000 family has been committed to open industry standards for software and hardware interfaces. The ARC specification of the ACE initiative is a new set of standards relevant to RISC workstation technology. This specification is based in large measure on DECstation 5000 technology, including the MIPS R3000A processor architecture, the TURBOchannel I/O interconnect, and the ULTRIX operating system. While the DS5000/240 is not completely ARC compliant, it is indeed ARC compatible. Software that now runs on the DS5000/240 will be binary compatible with future ARC platforms.

This overview presents a technical description of the DECstation 5000 Model 240 base system, focusing on the architectural features and implementation details that most contribute to its leading performance. The description briefly reviews the fundamental benefits of the RISC philosophy and shows why the MIPS R3000A architecture is an especially effective implementation of that philosophy.

The overview continues with a discussion of the system software, development software, and bundled applications that come with the DECstation 5000/240. The overview finishes with descriptions of the numerous graphics and multimedia options that may be used with the DS5000/240, as well as with other workstations of the family.

## 2 System Description

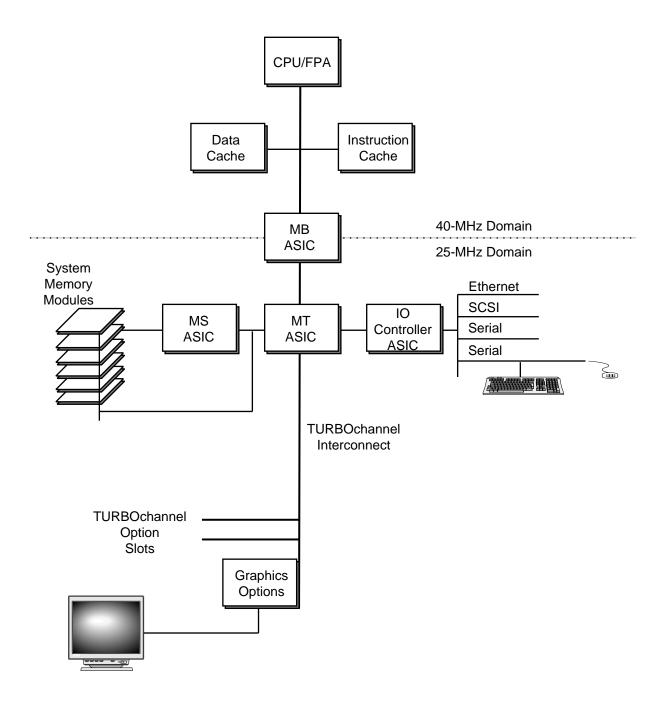

The DECstation 5000/240 is a desktop workstation comprising a system unit in a low-profile desktop enclosure, external keyboard, mouse, monitor, and, optionally, other external peripherals. The system unit includes the system module, CPU module, system memory, and I/O subsystem. The raster graphics output is provided by a TURBOchannel option card; several graphics output options are offered, as detailed in Section 4. The DS5000/240 also supports a large amount of external mass storage through a SCSI interface, and provides several other external interfaces, including Ethernet and serial devices. These several elements of the system are each discussed more fully in the subsequent sections. Figure 2.1 is a block diagram of the system.

## 2.1 Enclosure and Environmental Requirements

The overall exterior dimensions of the system enclosure are 20x17x3.6 inches. All I/O connectors, power switch, and line cord connector are located at the enclosure's rear bulkhead.

The power supply is dual voltage capable, so the system will run on either 110 or 220 volt line voltage, and at a line frequency from 47 to 63 Hz.

The DS5000/240 can be used in any ordinary office environment. The operating limits for ambient temperature are  $10^{\circ}$  to  $40^{\circ}$  C ( $50^{\circ}$  to  $104^{\circ}$  F).

## 2.2 CPU Subsystem

All DECstation 5000 models have a CPU based on the MIPS R3000A RISC architecture; the DS5000/240 uses the 40 MHz R3400 version of this processor architecture. This section begins with a review of the essential points of the RISC philosophy and its realization in the R3000A architecture. Then, Section 2.2.3 presents relevant details of the DS5000/240 CPU subsystem, the latest stage in the evolution of R3000-based RISC systems.

Figure 2.1 DECstation 5000/240 System Block Diagram

#### 2.2.1 The RISC Philosophy

The approach to computer design called RISC, Reduced Instruction Set Computer, has gained increasing currency through the 1980s. RISC technology now appears to dominate the workstation domain and is making inroads into the mainframe market as well. The term CISC, Complex Instruction Set Computer, is now sometimes used to distinguish the older ideas of processor design from RISC. Some of the essential characteristics that distinguish RISC from CISC are:

- smaller instruction sets

- less complex instructions

- no microcoded instructions

- few instruction formats

- uniform instruction byte length

- uniform instruction cycle count

- load/store architecture

- pipelined instruction execution

The first four of these characteristics have the obvious benefit of speeding up the computer design cycle, leading to lower computer cost, to quicker implementation of advances in the underlying circuit technology, and so to better performance in any technological era. The first two features may seem liabilities relative to functionality, but this is mitigated if the omitted complex instructions are rarely used in practice. In fact, most complex instructions that had been added to instruction sets for special purposes were rarely used in compiler-generated code.

Practical performance questions concern almost exclusively the use of high-level languages. Therefore, performance can be enhanced if the processor's instructions are designed to perform functions that are known from studies of compiler-generated code to be frequently required and that are easy and straight forward for compilers to generate. Rarely used complex instructions can be replaced by sequences of simple instructions without significantly harming overall performance.

The meaning of the seventh feature, load/store architecture, is that the processor should contain an ample number of registers and that all arithmetic and logical operands and results should be in registers. The only memory references are load and store instructions, which reduces the number of memory references and makes caching more effective.

The fourth through seventh features enable the eighth, pipelined instruction architecture. It is this feature that yields the greatest performance benefit of the RISC philosophy. In a pipelined instruction architecture, the execution of successive instructions overlap in time. To say the pipeline has depth d means that every instruction executes in the same number d of clock cycles and there are up to d instructions in the pipeline at any time. The instructions in the pipeline are at different stages of execution, each one stage behind the preceding one and advancing one stage per clock cycle. The result of pipelined instruction execution is a peak instruction execution rate of one instruction per clock cycle.

Of course, it is not always possible to keep the instruction execution pipeline full. For example, when memory references are needed, there will be a delay before the referenced item is available for use in an operation. And branch instructions introduce uncertainty in the order in which instructions should be started in the pipeline, not completely resolved until the branch instruction is executed. However, it is usually possible to fill the pipeline slots caused by branch delays or load/store delays by judiciously reordering instructions while respecting the data-dependency constraints. Keeping the instruction pipeline as full as possible is a job for an intelligent compiler. Thus, one element of the RISC design philosophy is to shift complexity from the processor architecture to optimizing compiler design. The success of RISC design rests in part on the advanced understanding of compiler optimization attained over the past few decades.

#### 2.2.2 The MIPS R3000A RISC Architecture

The MIPS R3000A architecture is a relatively mature implementation of RISC philosophy. The MIPS design was built on knowledge of earlier RISC efforts, especially the Stanford University RISC research work. MIPS started with the optimizing compilers from the Stanford effort, and studied the performance effects of variations in the instruction set through simulations of a range of applications compiled with the existing optimizers. The result of this approach is an instruction set that is very well tuned for high-level language use.

The basic R3000A CPU contains 32 general purpose 32-bit registers and ALU, Shifter, Multiplier/Divider, Address Adder, and Program Counter Increment/Mux. These registers are used for integer data and address arithmetic. In addition, the R3000A includes virtual memory management functions on the chip, using a translation lookaside buffer (TLB) and associated registers to provide very fast virtual-to-physical address translation.

Addresses have 32 bits, providing a 4-GB virtual address space. Only the first 2 GB of virtual memory are accessible to user processes; access to the higher 2 GB of the address space is reserved to the privileged kernel mode of the processor.

The kernel-reserved space is divided into three segments. One 512-MB virtual segment is not mapped through the TLB, but is always mapped directly to the first 512 MB of physical memory and is always cached. It is typically used for kernel executable code and some kernel data.

Another 512-MB virtual segment is also directly mapped to the first 512 MB of physical memory but is never cached. The operating system typically uses it for I/O registers, ROM code, and DMA buffers.

The remaining 1-GB segment of the kernel-reserved virtual memory space is mapped through the TLB and may be cached or not cached selectively on a per-page basis according to a bit in the TLB entry. The operating system typically uses this segment for stacks, user-page tables, and other per-process data that must be remapped on context switches.

The 2 GB of virtual address space available in user mode is always mapped through the TLB, but also may be cached or not selectively on a per-page basis.

The TLB is a fully associative memory with 64 entries, each mapping a 4-KB memory page. Each TLB entry includes the high-order 20 bits of the address of a virtual page, the high-order 20 bits of the address of the corresponding physical page, a 6-bit process identifier, and other bits used in virtual memory management, including the bit that controls whether references to the page are to be cached. A virtual address page number resulting from a processor address computation is immediately translated to the corresponding physical page number by the associative memory, provided that the page is in the TLB. Otherwise a TLB-miss exception occurs, causing software to load the TLB from memory-resident page tables, perhaps after fetching the page from disk if necessary.

The process identifier in the TLB entry allows up to 64 simultaneous processes to use the same virtual address space. This feature enhances the performance of the processor in multitasking environments such as the ULTRIX operating system.

The R3000A instruction set includes instructions for single- and double-precision IEEEstandard floating point operations, using 16 64-bit floating point registers. In earlier implementations of the R3000A architecture, the floating point instructions were provided by a coprocessor chip, the R3010 floating point accelerator (FPA). The integrated R3400 processor used in the DS5000/240 includes the FPA in the same VLSI package. The CPU, the memory management functions, and the floating point accelerator share local control logic, bus control logic, and a five-deep instruction pipeline. While the R3000A may be configured at boot time to operate with either byte order convention for memory words, the DECstations and the ACE/ARC specifications are exclusively little endian. That is, words are stored in memory with the least significant byte at the lowest address.

So that performance will not be limited by the bandwidth or access latency of the system memory, the R3000A relies on a fast cache memory. The R3000A architecture uses separate cache spaces for instructions and data. This division of cache has several advantages. The first advantage concerns locality of reference, that is, the probability that a series of successive memory references will all lie in a small region of the address space. Cache effectiveness depends essentially on locality of reference, and locality will clearly be greater for a sequence of instruction references only, or for a sequence of data references only, than for a mixture of instruction references and data references. A second advantage of the cache division is that it enables an architecture in which the processor can fetch one instruction and load one data word both in a single cycle, effectively doubling the maximum cache bandwidth. Further details on the DS5000/240 cache architecture and operation are given in Section 2.2.4.

#### 2.2.3 The DS5000/240 CPU Subsystem

The DECstation 5000/240 CPU subsystem comprises the R3400 CPU, with integrated floating point accelerator and virtual memory management, 64 KB each of instruction and data cache, the MB memory buffer custom ASIC, and the processor bus connecting these elements. This subsystem runs on a 40-MHz clock. The MB ASIC provides the interface and buffering between the 40-MHz time domain and the 25-MHz domain of the system memory and TURBOchannel.

The CPU subsystem plus the MT memory controller ASIC are located on a daughter card, measuring approximately 4.75x7.5 inches, plugging into the system module, and carrying integrated circuits on both surfaces. The user can expect the eventual possibility of upgrading the DS5000/240 by replacing the CPU subsystem daughter card with a more powerful one, possibly even an R4000-based CPU subsystem. Even prior to such an upgrade, the isolation of the higher-speed system on a daughter card has a cost benefit because it allows the use of two different kinds of PCB technology, the more expensive technology on the daughter card where required by the circuit speed, and the less expensive on the larger, slower system module.

## 2.2.4 Cache Architecture, Implementation, and Operation

The caches are direct-mapped, write-through caches, each containing 16K word entries. A cache word entry contains 32 bits of instruction or data, 16 tag bits, a valid flag bit, and byte-parity bits. The tag bits hold the high-order part of the physical address of the cached word in system memory. The low-order bits of the system memory address of the cached word are the same as its address in the cache; they form the cache index. (Physically, each cache entry contains a total of 60 bits; the unused bits are additional tag and parity bits needed in implementations with smaller caches.)

The dual cache is implemented in six static RAM components having a  $16K \ge 10$  bit  $\ge 2$  organization especially designed for providing one word from each cache in each processor cycle. In the R3000A architecture, each processor cycle may generate a data reference in the first half-cycle and an instruction reference in the second half-cycle.

On a write to a cached location, the data and the 16 high-order address bits are stored in the data and tag bits of the data cache location indexed by the 16 low-order address bits. (Note that this potentially changes the cache tag; that is, it may overwrite a cache of a different physical memory location with the same cache index.) At the same time, the address and data are latched into an eight-entry FIFO in the MB chip, where each entry contains 32 bits of data and 32 bits of address. On a write to an uncached location, the MB operates in the same way, but the cache is unaffected. The MB issues single-word writes to the memory subsystem, which can accept them at one word per 40-ns memory system cycle, that is, at 100 Mbytes/s maximum bandwidth. The MB can accept successive writes from the processor at one word per 25-ns processor cycle, so long as fewer than seven of the write FIFO locations are used; when seven FIFO locations are in use the MB asserts a signal that stalls the processor until writes to memory free some FIFO locations.

For a load or instruction fetch from a noncached address, the processor puts out the address, together with a *read memory* signal which causes the MB chip to perform a single-word read from the memory subsystem and pass the data back to the processor bus. This single memory read requires 690 ns.

For a load or an instruction fetch from a cached address, the processor puts the cache index onto the bus and the cache responds by putting the data and tag contained in the indexed cache entry onto the bus. If the cache tag matches the tag that the processor seeks, then the load or fetch has been completed in one cycle. Otherwise, it is a case of cache miss, and in the next cycle the processor puts out the complete desired address on the tag and index lines, along with the *read memory* signal that causes the MB chip to initiate a cache load.

A cache load fills eight consecutive cache words on an eight-word boundary. The MB contains dual eight-word buffers -- a read buffer and a prefetch buffer. For a cache load, the MB performs a page-mode read from memory to fill its read buffer, at one word per 40-ns memory system cycle after the 8-cycle page mode read latency. When the read buffer is full, the MB writes the eight locations to cache, in eight 25-ns CPU/cache cycles. When the cache line is on a 16-word boundary, the MB also fills the prefetch buffer, so that the next cache line can be available for a subsequent cache load without referencing system memory (unless one of the prefetched words is invalidated by a processor write to the location).

## 2.3 System Memory

The DS5000/240 uses a 512-MB physical address space and may contain from 8 to 480 MB of system DRAM memory. The physical addresses above 480 MB are used for system ROM, TURBOchannel, and I/O addresses. The memory is organized in 32-bit words and protected by an error correcting code (ECC), which can correct single bit errors and detect double-bit errors. The ECC code requires 7 additional bits for each 32-bit word.

The DRAM memory resides on 1 to 15 SIMM memory modules which plug into 128-pin connectors on the system module. Each memory module contains 39 DRAM chips, and so 8 MB if populated with 1-Mbit DRAMs and 32 MB if populated with 4-Mbit DRAMs. (All the memory modules in the system must contain the same size DRAMs.)

The memory modules use two-way low-order interleaving. That is, the even and odd word addresses are treated as separate banks whose access cycles run out of phase. This allows an effective maximum memory bandwidth of 100 Mbytes/s, double the maximum that could be achieved with a single-bank organization of the same DRAMs. Memory read latency is 320 ns for processor reads and 440 ns for TURBOchannel reads.

The MT custom ASIC serves as memory controller and interface between CPU subsystem, system memory, and TURBOchannel. The MT operates synchronously from the 25-MHz system clock. It interprets addresses issued by the MB ASIC, determining in which system memory module or TURBOchannel I/O space the addresses lie, and generating appropriate memory control signal sequences or TURBOchannel I/O transactions accordingly. It also performs DMA transactions.

The MT controller ASIC implements the ECC control, computing the check bits when storing a word to memory and checking them on a read. The MT also performs the DRAM refresh function.

The MS memory strobe ASIC functions to route the memory control signals from the MT to the correct memory module, according to the 4-bit module address lines from the MT. The MS provides 15 sets of MT memory control signals, one for each of the module connectors. For this function the MS replaces 16 integrated circuits used in the DS5000/200. The MS ASIC also generates the 25-MHz system clock, replacing three clock drivers used in the DS5000/200.

Memory access is resolved according to the following fixed priority:

- DRAM refresh cycles

- Processor access

- TURBOchannel slot 3 (the integrated I/O system)

- TURBOchannel slot 2 (option)

- TURBOchannel slot 1 (option)

- TURBOchannel slot 0 (option)

## 2.4 TURBOchannel I/O Interconnect

TURBOchannel is a high-performance, open I/O interconnect for desktop computers and servers, designed by Digital, and adopted by the ACE initiative as part of the ARC specification. TURBOchannel's outstanding performance is the consequence of its innovative architecture, which is specialized and optimized for the I/O function. The TURBOchannel architecture departs from the pure bus topology that has previously been the norm for small computer interconnections. Instead, the TURBOchannel control signals have a radial point-to-point topology; a TURBOchannel-based system provides separate control lines for each of several peripheral slots. The benefits of this architectural innovation are:

- simple, efficient protocol

- low signal count per option module

- low-latency transactions

- high-bandwidth DMA block transfer

- simplified option module design

The TURBOchannel is a synchronous channel, transferring one 32-bit word of data or protocol overhead in each cycle. The TURBOchannel protocol implements two kinds of transactions, DMA transactions and I/O transactions, each transferring data in either direction between the option and the system. In DMA transactions, the option transfers data directly between its buffers and system memory in blocks whose size is determined by the option, up to a maximum block size determined by the system (128 words in the DECstation 5000 Model 240).

TURBOchannel I/O transactions transfer single words of data between CPU registers and option memory locations. A load/store instruction referencing TURBOchannel address space causes the TURBOchannel control hardware to generate the TURBOchannel I/O transaction signal sequences for the appropriate TURBOchannel slot. I/O transactions are typically used for controlling the peripheral device, but they may also be used for data transfer by low-cost options lacking DMA buffers and logic.

See the TURBOchannel Technical Overview for more detailed discussion of the TURBOchannel architecture.

In the DECstation 5000/240, the MT memory controller ASIC is the hub of the TURBOchannel radial control logic. The MT provides control signals for four TURBOchannel slots. One TURBOchannel slot is dedicated to the integrated I/O subsystem implemented in the IO ASIC. The other three slots are for TURBOchannel options and are available through three 128-pin TURBOchannel connectors on the system module. The MT has four sets of lines for the four slot-specific TURBOchannel control signals. Five other TURBOchannel control signals, as well as the 32-bit TURBOchannel address/data bus, are common to all the TURBOchannel slots. DMA contention is resolved by the fixed-priority memory access rule and a rule that a TURBOchannel device must stall one cycle after completing a DMA transaction to avoid starving the other devices.

In the DS5000/240, each TURBOchannel slot is allocated 8 MB of the physical address space for option control registers and data buffers. TURBOchannel option ROMs in these address slots contain option-specific information used to configure the system at boot time.

The DS5000/240 TURBOchannel runs on the 25-MHz memory system clock and so has a maximum peak bandwidth of 100 MB/s. The overheads that the simple TURBOchannel DMA protocol imposes on the raw bandwidth are relatively small. Using the maximum 128-word DMA block size, and taking memory latencies and software overheads into account, DS5000/240 can sustain average TURBOchannel DMA transfer rates approaching 80 MB/s.

Double- or triple-width options occupy proportionally more space within the system enclosure, but they require only a single connector for the TURBOchannel signals. The TURBOchannel Extender (PMTCE) provides a method of recovering an internal TURBOchannel expansion slot if a 2-wide option is used internally, or of attaching a 2-wide or 3-wide option without covering more than one internal TURBOchannel option connector. The PMTCE enclosure can also accommodate two SCSI drives.

Section 2.6 discusses some of the available TURBOchannel options.

## 2.5 I/O Subsystem

The DS5000/240's I/O subsystem is based on a custom IO Controller ASIC. The IO ASIC is the same device that is used in the DECstation 5000 Model 100 series, but it runs at 25 MHz in the DS5000/240, twice the Model 100 series frequency. This device interfaces the TURBOchannel interconnect on one side to several different devices on the other side, mostly controllers for particular types of peripherals or data communication interfaces. Specifically, in the DS5000/240, the IO ASIC supports interfaces to:

- Serial ports (up to four RS-232 devices)

- SCSI controller (up to seven SCSI devices)

- Ethernet

- Realtime clock

- System ROM

The IO ASIC and the several peripheral controllers communicate on a 16-bit data bus. In addition, the IO ASIC uses a number of specific control lines to the various devices. The I/O subsystem supports DMA transfer for Ethernet, SCSI, and the serial ports.

## 2.5.1 Serial Ports

Two dual UARTs support the keyboard, mouse, and two communication ports for optional serial peripherals. Each serial line supports baud rates from 50 baud to 208.4 Kbaud. The communication ports support modem control signals, but are also for the use of local peripherals such as dial and button box, graphics tablet, or track ball. The electrical signal levels conform to the EIA-232-D standard.

The keyboard and mouse are connected to a single DB115 connector. Each communication port uses a B25 connector.

## 2.5.2 SCSI Interface

The DS5000/240's SCSI (Small Computer System Interconnect) interface conforms to the ANSI SCSI-2 standard, and so is compatible with a wide range of SCSI devices available from Digital and third parties. The SCSI controller can perform asynchronous or synchronous data transfers, at up to 5 MB/s, with DMA access through the IO ASIC.

SCSI is the primary means of connecting disks, tape drives, and CD-ROM devices to the system. The SCSI connector at the back of the system enclosure provides for connecting up to seven SCSI devices on a daisy-chain cable. Some of the particular devices available from Digital and appropriate for use with the DS5000/240 are:

| • | RZ23:  | 104 MB   | 3.5-in hard disk    |

|---|--------|----------|---------------------|

| • | RZ23L: | 121 MB   | 3.5-in hard disk    |

| ٠ | RZ24:  | 209 MB   | 3.5-in hard disk    |

| ٠ | RZ25:  | 426 MB   | 3.5-in hard disk    |

| • | RZ55:  | 332 MB   | 5.25-in hard disk   |

| • | RZ56:  | 665 MB   | 5.25-in hard disk   |

| • | RZ57:  | 1.0 GB   | 5.25-in hard disk   |

| • | RZ58:  | 1.38 GB  | 5.25-in hard disk   |

| • | RRD40: | 600 MB   | CD-ROM disk         |

| • | RRD42: | 600 MB   | CD-ROM disk         |

| • | TK50Z: | 95 MB    | tape cartridge      |

| • | TSZ05: | 1600 BPI | 9-track tape        |

| • | TZ30:  | 95 MB    | tape cartridge      |

| • | TZK10: | 525 MB   | QIC tape            |

| • | TLZ04: | 1.2 GB   | RDAT tape           |

| • | TKZ08: | 2.2 GB   | 8 mm tape           |

| • | RX23:  | 1.4 MB   | 3.5-in floppy disk  |

| • | RX33:  | 1.2 MB   | 5.25-in floppy disk |

|   |        |          |                     |

#### 2.5.3 Ethernet Interface

The DS5000/240 supports thick-wire Ethernet via a 15 pin DSUB connector. ThinWire and twisted pair Ethernets can be accommodated with available adapters.

## 2.6 TURBOchannel Options

Digital and third parties offer a growing family of TURBOchannel option boards. Available from Digital, in addition to the graphics and multimedia options described elsewhere in this overview, are:

- SCSI controller

- Ethernet interface

- Fiber Distributed Data Interface (FDDI) controller

- VMEbus adapter

- Token Ring controller

TURBOchannel products presently available from third parties include options for X.25 and other communications interfaces, RAID disk controller, film recorder, very high-resolution raster displays, array processors, WORM drive controllers, and others.

Now that TURBOchannel has been adopted by the ACE initiative, the universe of TURBOchannel devices can be expected to grow rapidly. Contact the Digital TRI/ADD Program for an up-to-date list of available TURBOchannel options from Digital and third-party vendors.

## 2.7 CPU Performance Measurement

A number of different factors contribute to the CPU performance perceived by the user: processor clock speed, cache efficiency, memory bandwidth and latency, as well as software issues such as compiler optimization efficiency. To the user, the most relevant performance characterization is in terms of average instructions-per-second or operations-per-second as measured for a suite of benchmark programs which fairly represents the user's intended workload, specified in the user's preferred source language, and built with the supplied development software. The performance numbers given in this section result from industry-standard benchmark suites, using new compiler technology which will be available to DECstation users.

To facilitate the comparison of systems from diverse vendors, the System Performance Evaluation Cooperative (SPEC) has defined a suite of programs deemed typical of scientific and technical applications. There are separate programs for integer and for floating point performance characterization. The results are expressed as ratios of the performance to that of a VAX 11/780; the quoted numbers are geometric means of these ratios over the several programs in each suite.

The measure SPEC ratings for the DECstation 5000/240 are:

| SPECmark | 32.4 |

|----------|------|

| SPECint  | 27.9 |

| SPECfp   | 35.8 |

The Dhrystone (Version 1.1) benchmark suite is somewhat older than the SPEC suite and tends to emphasize integer arithmetic. With this suite, the DS5000/240 rates at 42.9 million instructions per second (MIPS). Again, the reference machine is a VAX 11/780 which rates 1 MIP on this benchmark.

Another floating point benchmark, current as a standard test in supercomputer performance rating, is based on Linpack, a linear algebra package widely used in scientific applications. The DS5000/240's Linpack ratings for a 100x100 linear system solution are 10.8 single-precision megaflops (MFLOPS) and 6.0 double precision MFLOPS.

The performance of the several graphics options available for the DECstation 5000/240 are given in Section 4.6.

## 3 System Software

The DECstation 5000 system software environment is based on open industry standards, and provides binary compatibility across the entire line. Adherence to open standards promotes portability of applications among systems from different vendors, thereby protecting the user's investment in software and training. Open standards also enable interoperability of systems from different vendors, which becomes more important as the connectivity of computing environments continually grows.

Digital is a leader in the development of new industry standards and integrates emerging standards into its software products. Digital develops system software according to the X/Open<sup>TM</sup>, IEEE POSIX, and Open Software Foundation<sup>TM</sup> (OSF<sup>®</sup>) specifications. Digital is one of the founding members of the ACE initiative. The existing Digital system software provides a basis for a large part of the ARC specification under ACE. While the DECstation 5000/240 does not fully implement the ARC specification, it is ARC compatible. Software that runs now on the DS5000/240 will be binary-compatible with future ARC-compliant platforms.

## 3.1 ULTRIX Operating System

The operating system for all DECstations is ULTRIX, Digital's enhanced native implementation of the industry-standard UNIX<sup>®</sup> operating system. ULTRIX is a general-purpose, multiuser, multitasking, interactive system conforming to IEEE standard 1003.1-1988 (POSIX) and to the Common Applications Environment as defined by the X/Open Portability Guide 3.

ULTRIX includes the features of BSD (Berkeley Software Distribution) 4.3 and is source-level compatible with SVID (AT&T<sup>®</sup> UNIX System V<sup>®</sup> Interface Definition) Issue 2. But ULTRIX goes beyond these standards and offers many unique features, commands, and programming languages. For more information on ULTRIX functionality and conformance to industry standards, see the ULTRIX Handbook (EC-H0592-43).

The next major release of ULTRIX software will be based on the Open Software Foundation's OSF/1<sup>®</sup> operating system, which is also the basis for SCO<sup>®</sup> Open Desktop<sup>®</sup>, the UNIX specified for ARC/ACE. This system is specified to include an efficient virtual memory system, shared libraries, POSIX threads, a System V-compatible streams framework, dynamic subsystem loading, advanced security features, and comprehensive support for internationalization.

## 3.2 Software Development Environment and Compilers

A rich environment for software development has been a hallmark of UNIX since its inception. Throughout the evolution of UNIX, its editors, compilers, build utilities, and source-control systems have often represented the leading edge of software development technology. Digital's RISC/ULTRIX software development environment continues the tradition, and makes important new contributions to its further advancement.

#### 3.2.1 Languages and Compiler Technology

Digital provides a full set of language compilers for the RISC/ULTRIX software development. Compilers developed by Digital include:

- DEC Ada

- DEC C

- DEC C++

- DEC FORTRAN

- DEC Trellis

- Pascal for RISC

The Digital-developed compilers conform to applicable language standards where they exist.

Compilers developed by third parties but supported by Digital as Digital Distributed Software include:

- pcc (MIPS C)

- MicroFocus COBOL/2

- Lucid Common LISP

For several of these languages and some other languages, including BASIC, alternate compilers for RISC/ULTRIX are available from third-party vendors.

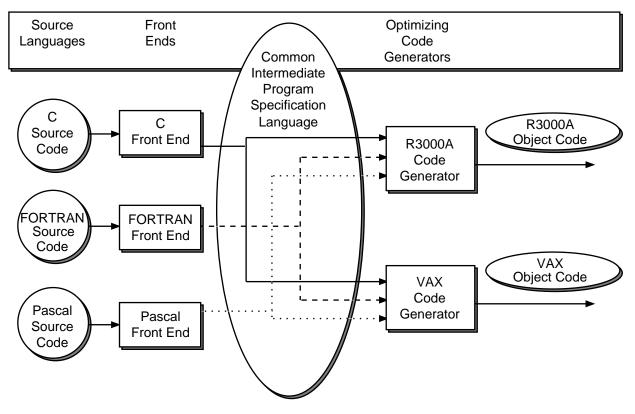

Modern compilers are typically made up of two distinct parts: (1) a front end, which accepts the source code as input and parses the source language, but is independent of the target processor; and (2) a back end, which generates optimized machine code for a particular target processor, but is independent of the source language. The output of the front end, which is the input to the back end, is in an intermediate program specification language, which is independent of both the source language and the target machine architecture. A common intermediate language may be used for several different source languages and machine architectures. In this way, the benefits of optimizing the back end for a particular machine architecture can be enjoyed in several languages. Each language front end is used on several machine architectures, ensuring a common language definition and application portability. Figure 3.1 illustrates compiler architecture.

Figure 3.1 Compiler Architecture

Section 2.2.1 pointed out that compiler optimization is an essential element of the RISC philosophy, especially with regard to keeping the RISC instruction pipeline full. Optimizing generated code for the RISC processor is a function of the compiler back end, so it is natural that a number of compilers use the code generator that was developed at MIPS hand-in-hand with the design of the processor architecture. However, Digital has embarked on its own RISC compiler development program. The DEC FORTRAN and DEC Ada compilers for RISC use Digital's new proprietary R3000A code generator (and intermediate language), which generates substantially faster code, as much as 15% faster for some applications.

#### 3.2.2 DEC C++ and Object-oriented Software Development

C++ is a programming language derived from the C language. It was developed at AT&T and has gained increasing favor in the last few years. C++ has a number of features that are improvements over C, but its most important distinguishing feature is its support of the *class* concept, which is central to the methodology of *object-oriented* programming. "Object oriented" refers to a complex set of ideas of software construction -- modularity, data abstraction, strong typing, encapsulation, messaging, information hiding, inheritance -- whose disciplined application can reduce programming errors and produce software that is more robust, understandable, extensible, and reusable.

DEC C++ implements the most advanced version of the C++ V3.0, as defined in the Annotated Reference Manual<sup>1</sup> written by the developers of the language. This version is the starting point for the ANSI standardization effort, in which Digital is an active participant.

DEC C++ is implemented as a native compiler, unlike the AT&T and other implementations that use pre-processors to translate C++ source to C code. It includes a C++ source-level debugger, which supports all the advanced features of the language and which can be used either with a *dbx*-like command line user interface or a with a graphical user interface within the DEC FUSE facility, described in the next section.

One of the most advantageous features of DEC C++ is its incremental linker, which processes only the modified modules on any link. Incremental linking can be three to seventy times faster than the conventional ULTRIX linker.

DEC C++ also comes with encapsulated reusable code in the form of class libraries, both the standard Class Libraries and additional class libraries developed by Digital. Digital has an on-going program for extending the available class libraries for C++.

Digital offers an alternate object-oriented programming method in DEC Trellis. Trellis is a programming language, a development environment, and set of class libraries. One way in which the Trellis approach differs from that of C++ is that Trellis is a pure object-oriented language, while C++ is C with considerable object-oriented technology added to it. It is possible to use C++ without an object-oriented programming style, but the use of Trellis enforces an object-oriented discipline. DEC Trellis can exchange calls with DEC C++, so it is possible to have the best of both object-oriented worlds.

<sup>1</sup> For more information on C++, the following books are recommended:

- The initial definitive specification of the language was given in the book by Bjarne Stroustroup, *The C++ Programming Language*, Addison Wesley, 1986.

- The definition of Version 3.0, which is the basis for the standardization effort is in the book by Bjarne Stroustroup and Margaret Ellis, *The Annotated* C++ *Reference Manual*, Addison Wesley, 1991.

For an excellent discussion of the theory of object-oriented programming, independent of the C++ language, see the book by Bertrand Meyer, *Object-Oriented Software Construction*, Prentice-Hall, 1988.

## 3.2.3 DEC FUSE

DEC FUSE is an ULTRIX-based, integrated, graphically-oriented, multi-language software engineering environment. The introduction of the DECstation 5000/240 is contemporary with the release of DEC FUSE Version 1.1. The supported languages include C, FORTRAN, Pascal, and C++. FUSE is based on UNIX commands and utilities traditionally associated with programmer productivity and provides a set of Motif<sup>®</sup>-based graphical tools. It makes extensive use of dynamic graphical capabilities to provide visual representations of a program's structure.

DEC FUSE includes its own editor, but also supports the GNU Emacs and vi editors. DEC FUSE includes a GUI-based debugger, a Program Builder, a Call Graph Browser, a Profiler, a Cross Referencer, a C++ class browser, a code management system, and extended annotation support. Another advanced feature is support for distributed build, that is, using several work-stations on a network in parallel for compiling and linking large builds.

DEC FUSE EnCASE is a facility that allows developers and end-users to integrate additional development tools into DEC FUSE. The tools added to DEC FUSE by means of EnCASE can be third-party software development products or home-grown UNIX utilities. Tools added to the DEC FUSE environment can be linked with existing DEC FUSE tools or with other newly added tools to enhance existing work procedures. DEC FUSE EnCASE uses object-oriented messaging principles to manage the integration of tools.

## 3.3 DECwindows and Graphical User Interfaces

Virtually all users of workstations and personal computers are now familiar with the use of a window system to work with several applications at the same time. Each window serves as a virtual graphics terminal to receive the output of an application or utility. Most window systems provide the convenience of transferring data between applications by interactive "cutting and pasting" in the corresponding windows.

The window system must be common to all the concurrent applications, and so forms part of the system software, placed between the operating system and the applications. A central software element is the window manager, which resolves contention for display area among the different applications and gives the interactive user a measure of control over the window layout. The window manager is also concerned with associating operation of a single keyboard or pointing device with input for particular applications, identified with windows.

Window systems also serve as platforms for graphical user interfaces (GUI), in which interactive users enter input by directly manipulating screen objects -- buttons, menus, scroll bars, dialogue boxes -- by pointing and clicking with mouse and cursor. If a number of applications are constructed using the same GUI, that is, a common set of interactive screen objects and a common style of manipulating them, then they are all easier to learn and use.

#### 3.3.1 DECwindows

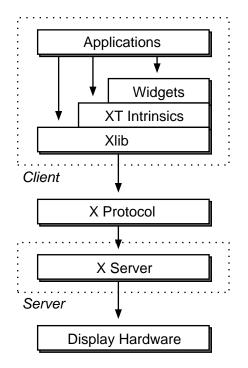

The X Window System (also called X or X11) is an industry-standard networked window system developed at Massachusetts Institute of Technology with financial and technical support by an industry consortium of which Digital is a leading member. It is a networked window system constructed according to a *client/server* model. The server is the software that has control of the interactive graphics workstation -- the display and the associated interactive input devices. The client is an application that carries on interactive I/O through requests to the server. The client may run on the same processor as the server, or it may reside on a remote host and communicate with the server over a network.

The X client and server communicate through a precise protocol, the X Protocol, which is designed for communicating simple graphics and window control information. In case the client and server are on different hosts, the X Protocol is implemented over the underlying network protocol. The protocol is independent of the system architecture and operating system on both ends. Therefore, the X Protocol supports interoperability for transparent network graphics among diverse systems.

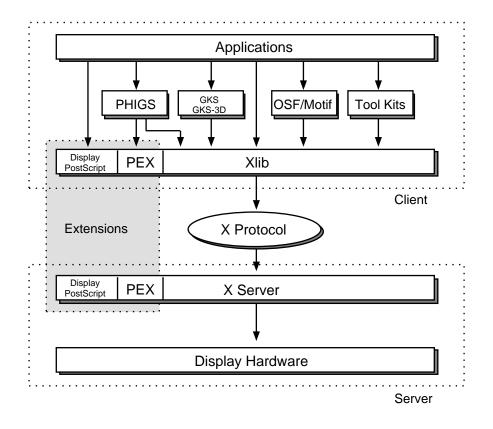

The X software architecture has two parts, the server and the client-side support. The graphical device dependence is all in the server; the client side is device independent. The basic application programming interface on the client side is *Xlib*, a library of almost 400 routines for 2D graphical primitives, window management functions, and input event management. Xlib is the lowest level access that an application programmer has to the X Window System.

The standard X Window System also provides a higher-level programming interface, the tool kit *Xtk*, which provides the programmer with tools for constructing and managing interactive screen objects, such as buttons and sliders, called *widgets* in X. Xtk comes with a set of widgets, called the *intrinsics*, but it defines no policy on look-and-feel standards. It can be used to implement graphical user interfaces with particular look and feel, some of which are discussed further below in Section 3.3.2. Figure 3.2 illustrates the architecture of the X Window System.

DECwindows is Digital's enhanced implementation of the X Window System. Some of Digital's enhancements to the standard system are: faster algorithms, international keyboard support, better security features, and additional language bindings. On the DECstation 5000 series workstations, DECwindows is an exceptionally fast and robust implementation of X. The version of DECwindows shipped with ULTRIX 4.2A embodies the X11R4 version of the X Window System.

Figure 3.2 X Window System Architecture

#### 3.3.2 OSF/Motif and VUIT

OSF/Motif<sup>®</sup> is an industry-standard graphical user interface adopted by the Open Software Foundation and based largely on XUI, the DECwindows GUI originally developed by Digital. OSF/Motif includes a tool kit for constructing interactive widgets, a user-interface language (UIL) for building applications with Motif user interfaces, and a style guide. Through adherence to the style guide, the application programmer can be sure that the application will have a standard look and feel, which will make it easy to learn and use by a user familiar with other Motif-based applications.

The ULTRIX operating system for the DECstations includes both OSF/Motif and XUI. The window manager for the former is called *mwm*; the window manager for the latter is called *dxwm*.

DEC Visual User Interface Tool (VUIT) is an interactive, WYSIWYG-style editor for building standard OSF/Motif application interfaces. VUIT provides an environment to rapidly develop, test, and modify graphical user interfaces for Motif-based applications. VUIT is a GUI for building GUIs; the application programmer uses VUIT to create his GUI by pointing, clicking, and dragging. VUIT writes and reads standard OSF/Motif UIL files, so it can be used to edit GUIs constructed without the use of VUIT. Interfaces designed with VUIT automatically conform to OSF/Motif Style Guide policies. VUIT is optionally available on all DECstation systems.

## 3.3.3 Extensions to the X Protocol: PEX, Display PostScript, and Xv

The standard X Protocol does not include semantics for addressing all conceivable functionality that a graphics server may provide. When new graphical functionality is added to the server side, then it becomes necessary to extend the protocol and the server code in order to be able to use the new functionality in the context of the X Window System. The design of the X Window System anticipated the need for such extensions and provides a standard way of making them.

For example, the graphical content of the original X Protocol is limited to two-dimensional graphics. However, some graphics subsystems, such as the PXG family of options discussed in Section 4.5, provide hardware and firmware for 3D graphics processing. The graphics subsystem is clearly on the server side of the X Protocol. In order to be able to use 3D hardware to make pictures in X windows, the X Consortium has defined *PEX*, a standard extension to the X Protocol. The name "PEX" stands for "PHIGS Extension to X" to reflect the fact that the semantics of PEX are based largely on PHIGS, the ANSI/ISO standard 3D graphics application programming interface (API), discussed in Section 3.4.2. However, PEX is just a protocol for communicating 3D graphics information between client applications and 3D graphics servers; it can also be used with other graphics APIs.

Implementation of a PEX server on 3D graphics hardware makes the hardware available for network-transparent, inter-vendor distributed applications. Digital has been a leading member of the PEX development and standardization effort, and produced the industry's first PEX-based workstation in 1989. The Digital PEX server is bundled with the 3D acceleration options discussed below in Section 4.5.

A second extension of the X Protocol has been developed by Digital to support the Display PostScript<sup>®</sup> graphics API described below in Section 3.4.1. This extension has been adopted as a standard by the X Consortium.

Digital has worked with MIT to develop yet another extension to the X Protocol, called Xv, for support of the DECvideo multimedia options discussed in Section 5. Digital is actively working towards having Xv adopted as a standard by the X Consortium.

## 3.4 Graphics Programming Interfaces

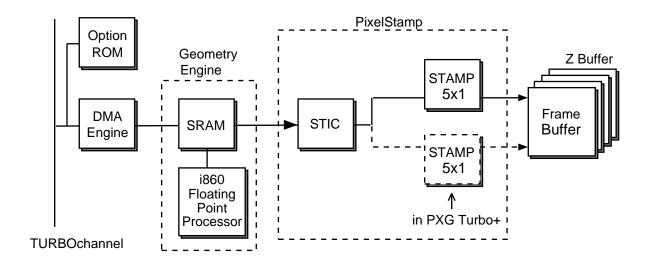

The Xlib API, mentioned in Section 3.3.1, provides drawing primitives only for simple 2D figures such as lines, arcs, polygons, and text. To support development of both 2D and 3D applications, programmers need much richer and higher-level APIs for defining, manipulating, editing, displaying, and storing complex graphical objects. Digital offers several additional higher-level graphics APIs both for 3D graphics and for 2D applications that need more graphics primitives and richer graphical data structuring capabilities. For display I/O, all of these higher-level APIs work through the X Window System and its extensions. Figure 3.3 depicts the architecture of the graphics programming environment supported on the DECstations.

Figure 3.3 Graphics Programming System Architecture

## 3.4.1 Display PostScript

*PostScript* is a page description language, developed by Adobe Systems Inc., which has become the industry-standard means of access to the advanced graphical and typographical capabilities of laser printers. *Display PostScript* is a language for programming interactive raster displays, adapted from PostScript. Digital's implementation of the Display PostScript interpreter is licensed directly from Adobe and is complete and fully compatible.

As mentioned above in Section 3.3.3, Digital has implemented the Display PostScript interpreter as part of the X Server, and extended the X Protocol to access it. Server-side implementation of the Display PostScript interpreter has certain advantages concerning performance and compatibility. But, just as PostScript is frequently implemented by a PostScript engine within a laser printer, it is natural to anticipate the advent of Display PostScript acceleration hardware in workstation displays, which will then *require* server-side implementation and protocol extension. By taking the lead in developing server-side implementation and standardization of the protocol extension, Digital ensures future compatibility of Display PostScript applications written today.

## 3.4.2 DEC PHIGS and PEXIIb

*PHIGS* (Programmer's Hierarchical Interactive Graphics System) is the preferred ANSI/ISO standard API for 3D device-independent graphics. *PHIGS PLUS* is a proposed extension to the standard, which adds advanced surface primitives and lighting-and-shading rendering capability to the original PHIGS system. At the time of this writing, the PHIGS PLUS extension is close to final adoption; after adoption, the term "PHIGS" will be understood to include the PHIGS PLUS extension.

Standard PHIGS is a *structure-oriented* (as opposed to an *immediate-mode*) API. That is, through calls to the API library functions, the application builds data structures representing the picture to be drawn, structures which are retained and stored by the PHIGS runtime system and which can be redisplayed through subsequent calls. PHIGS structures admit hierarchical organization and structure editing, two important features that help distinguish PHIGS from the GKS and GKS-3D standards discussed in Section 3.4.3.

DEC PHIGS is a very complete implementation of PHIGS, including the proposed PHIGS PLUS functionality and several further extensions. The advanced PHIGS PLUS features of DEC PHIGS include lighting, shading, depth cueing, and non-uniform rational B-spline (NURBS) curves and surfaces. The further extensions include circle and arc primitives, an immediate-mode feature, and certain other extensions that are not part of the standard but advocated and informally encouraged by a group of CAD/CAM software companies. DEC PHIGS offers C and FORTRAN language bindings, but also supports PHIGS programming in several other languages.

DEC PHIGS is very well integrated with DECwindows and provides the programmer with several different choices for managing the interaction between PHIGS and X and for mixing PHIGS calls and Xlib calls. Further, DEC PHIGS can generate PEX protocol requests (see Section 3.3.3) to make use of hardware graphics acceleration. Alternatively, PHIGS can perform 3D graphics processing in software to generate drawing requests through the ordinary X Protocol. A few of the more compute-intensive capabilities of PHIGS PLUS are provided only when supported by 3D hardware acceleration. Still, the RISC processing power available in the DECstations enables practical 3D applications through DEC PHIGS without 3D acceleration, so long as such features as smooth shading and hardware Z buffering are not needed.

The PHIGS runtime support is bundled with the PXG, PXG+, and PXG Turbo+ graphics options and is optional on other configurations. The DEC PHIGS development system is optional on all DECstations.

PEXlib is a 3D graphics API that allows programmers to access the PEX protocol at a slightly lower level than PHIGS, analogous to the Xlib API to the X Protocol. PEXlib has no status as a standard, but it will be of interest to programmers who wish to avoid some of the overhead of PHIGS and have a little more direct control of the PEX server. PEXlib will ship for the first time with DEC PHIGS 2.3.

## 3.4.3 GKS and GKS-3D

*GKS* (Graphics Kernel System) is an ISO standard for a 2D graphics API, which was originally developed in Europe and predates PHIGS. *GKS-3D* is an extension of the standard to include 3D geometry. However, GKS-3D does not include the advanced primitives and lighting-based features of PHIGS PLUS.

Digital's implementation DEC GKS-3D supports full level 2c functionality of the standard, and is upward compatible with the DEC GKS implementation. GKS and GKS-3D are optional products for the DECstation 5000 family.

While GKS and GKS-3D have a kind of retained structures (called *segments*), they lack the hierarchical structuring and structure-editing features of PHIGS, and the lighting and shading capabilities of PHIGS PLUS. Strictly 2D graphics applications can sometimes enjoy better performance when implemented in GKS than in PHIGS, because PHIGS is intrinsically 3D internally and therefore carries some 3D overhead even when used for 2D applications.

## 3.5 Networking Software

Connectivity, interoperability, open networking, and distributed applications have become normal and expected features for workstation installations in industrial, commercial, and academic environments. DECstations provide the full range of options for connectivity, both in Digital's proprietary network and in multivendor open networking situations. Ethernet support through the I/O subsystem is standard on the DECstation 5000/240. In addition, connections to Fiber Distributed Data Interconnect (FDDI) and IBM<sup>®</sup> Token Ring are available through TURBOchannel options. These networking possibilities are all supported by available software.

## 3.5.1 TCP/IP

The TCP/IP network protocol is a set of software communications protocols, which were developed in government and defense contractor installations, and are now widely used in many networking environments. In DECstation workstations, TCP/IP is the protocol by which the Ethernet networking hardware is used. TCP/IP has become a *de facto* standard in UNIX operating environments and is an integral part of the ULTRIX operating system, supporting such facilities as remote login (*rlogin*), remote copy (*rcp*), and file transfer protocol (*ftp*), as well as the Network File System (NFS<sup>TM</sup>), discussed in Section 3.5.2.

TCP/IP is not limited to UNIX systems and can be used with other operating systems. In particular, DECstations can use TCP/IP to communicate with VMS systems using the FUSION TCP/IP product.

#### 3.5.2 Network File System

The ULTRIX operating system supports the NFS, an industry-standard facility that governs file sharing among networked systems. NFS allows a workstation user to access disk storage on a remote file server as if it were local, and provides a network administrative service called Yellow Pages. NFS comes standard with ULTRIX on all DECstation workstations. In the future, the OSF/Distributed Computing Environment (DCE) will provide NFS interoperability as well as significantly enhanced file services.

## 3.5.3 DECnet/OSI

DECnet is Digital's optional networking product that implements the Open Systems Interconnect (OSI) model. DECnet provides communication among both RISC- and VAX-based UL-TRIX systems as well as VAX/VMS systems. DECnet offers task-to-task communications, establishing logical connection to other DECnet nodes in the network, remote file transfer, mail, coexistence with the Internet protocols on TCP/IP-based machines, and network-wide resource sharing and management.

## 3.5.4 Network Application Support

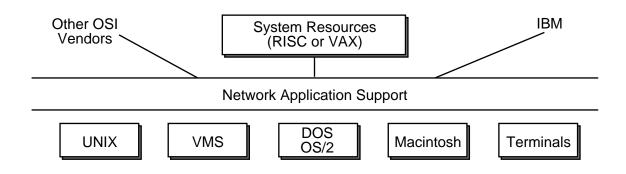

Network Application Support (NAS) is a backbone set of application services that allows integration of multiple applications in a distributed, multivendor environments. A NAS application can, for example, combine graphics from an Apple<sup>®</sup> Macintosh<sup>®</sup>, a Lotus<sup>®</sup> spreadsheet from a DOS PC, a drawing from a DECstation, data from an IBM mainframe, and a scanned image from a VAXstation all into a single report that can be sent electronically to others anywhere on the network. Figure 3.4 illustrates NAS architecture.

Figure 3.4 NAS Architecture

NAS consists of well-defined industry-standard programming interfaces, tool kits, and products that help developers build applications that are well integrated and easily portable across diverse systems. Some of the components of NAS are:

- ULTRIX/SQL, an industry-standard relational database management system with a Structured Query Language (*SQL*) interface. The ULTRIX/SQL runtime library and license are bundled with the ULTRIX operating system.

- Remote Procedure Calls (*RPC*), which allow remote execution over loosely coupled CPUs in a heterogeneous network. DEC RPC is based on the Network Computing System (NCS) from HP/Apollo, and is bundled with the ULTRIX operating system.

- Personal Computing Systems Architecture (PCSA), Digital's PC integration software that combines DOS or OS/2<sup>®</sup>-based PCs into a PC Local Area Network or corporate computing network.

- IBM 3270 terminal support and access to IBM environments through the DECnet/SNA family of IBM interconnect products.

- DECwindows, Digital's implementation of the X Window System (see Section 3.3.1).

- Compound Document Architecture, a method for creating, storing, and exchanging files that contain a number of integrated components including text, synthetic graphics, and scanned images.

## 3.6 Application Software

The DECstation 5000/240 is binary compatible with the rest of the DECstation 5000 family and so enjoys the benefit of the large repertoire of application software that has been written for or ported to the DECstation 5000 architecture. In particular, many of the major third-party CAD packages and visualization tools have already been ported to the DS5000/200 and the accelerated graphics options; these will all run on the DS5000/240 and the new graphics options with substantially improved performance.

In addition, to these high-end applications, the DS5000/240 user can run a wide range of the popular desktop productivity packages that have been the mainstay of the personal computer industry. Many of these packages also have already been ported to the DECstation 5000 family. Further, DEC SoftPC for ULTRIX is a software emulator of the IBM PC/AT<sup>TM</sup> class of personal computer, which will allow running the object code of most MS-DOS<sup>®</sup> applications.

See ULTRIX Software Source Book (EC-J1284-43) for listings of available technical and commercial applications.

# **4** Graphics Options

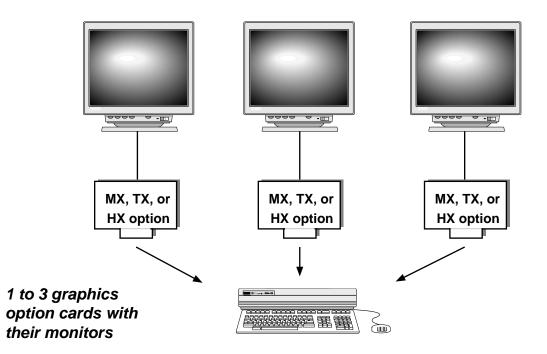

Digital offers a wide range of TURBOchannel-based graphics options, which are applicable to all the DECstation 5000 models. Several new options are introduced at the same time as the DECstation 5000/240. Two new options are higher-performance versions of earlier architectures and two have new architectures. All of the graphics options are TURBOchannel options, taking one to three TURBOchannel option slots. Table 4.1 summarizes the relevant characteristics of the TURBOchannel-based graphics options. Section 4.6 summarizes relevant graphics performance characteristics of the DS5000/240 system paired with several of the options.

The MX and PXG options were previously available. The new options are the HX,TX, PXG+, and PXG Turbo+.

| Options    | Resolution                        | Depth       | Refresh        | Tc Slots | Acceleration Notes                                                           |

|------------|-----------------------------------|-------------|----------------|----------|------------------------------------------------------------------------------|

| MX         | 1280x1024                         | 1           | 72 Hz          | 1        | None                                                                         |

| нх         | 1280x1024<br>1024x864<br>1024x768 | 8           | 72/66/60<br>Hz | 1        | X primitives; Smart Frame Buffer;<br>Fast Tc IF                              |

| ТХ         | 1280x1024                         | 24+8+1      | 72/66 Hz       | 1        | None; supports DECvideo                                                      |

| PXG        | 1280x1024                         | 8/24+DB+24Z | 72/66 Hz       | 2        | Scan conversion; optional Z buffer (for<br>8-plane versions) and 3D geometry |

| PXG+       | 1280x1024                         | 8/24+DB+24Z | 72/66 Hz       | 2        | Scan conversion; optional Z buffer (for<br>8-plane versions) and 3D geometry |

| PXG Turbo+ | 1280x1024                         | 24+24+24+24 | 72/66 Hz       | 3        | Scan conversion; two pixel stamps                                            |

**Table 4.1 Graphics Options Summary**

## 4.1 Graphics Options Overview

This section sets the stage by introducing features common to all the graphics options and by discussing some of the ways in which graphics options differ. The subsequent sections present details on each of the available options.

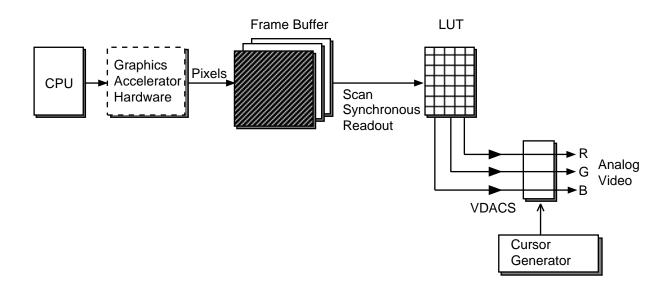

Raster graphics systems are built around a *frame buffer*, which is a memory containing a pixellevel description of the displayed image and is used to refresh the raster display. Refreshing the display involves clocking out the frame-buffer data synchronously with the sweep cycle of a cathode ray tube (CRT) monitor, using the pixel values to produce the analog signals that drive the color guns of the CRT. Frequently, the frame buffer is implemented in a special kind of dual-ported RAM, called video RAM (VRAM), which allows the CPU or graphics processing hardware to draw in the picture by writing to the frame buffer without interfering with the refresh cycle. Figure 4.1 depicts a "generic" raster graphics system. The box labeled *Graphics Accelerator Hardware* may be absent or may take any of several different forms. The HX option and the PXG family options illustrate two different graphics acceleration architectures.

Figure 4.1 Generic Raster Graphics System

The number of bits per pixel in the frame buffer is called its *depth*. If the depth is *d*, then the maximum number of different colors or intensities that the display can simultaneously contain is  $2^d$ : specifically, 2 colors when d=1, and 256 colors when d=8. About 16.7 million different colors are possible when d=24, but the maximum number of simultaneous colors is, of course, limited by the number of pixels, and this is somewhat less than 16.7 million for all of the graphics options.

On most 8-bit color systems and many 24-bit color systems, the pixel values are used as indices into a color lookup table whose entries determine the red, green, and blue (RGB) components of the color actually displayed. Typically, the lookup table entries each contain 24 bits, eight bits for each of the red, green, and blue components. The color lookup table entries are themselves under software control. Thus, when d=8, the lookup table has 256 24-bit entries, so the 256 different colors that can be simultaneously displayed at any moment are selected from a palette of 16.7 million colors.

A 24-bit system that has no color lookup table (such as the TX option) is called a *true-color* system. The 24 bits at each pixel are partitioned into three 8-bit fields, which directly determine the RGB values for the pixel. In 24-bit systems that have color lookup tables (such as the PXG family options), there are three 256-entry x 8-bit lookup tables, which allow remapping of each of the color components independently. Such remapping of color components is frequently referred to as *pseudo-color*.

Many frame buffers have additional *bit planes* (bits per pixel), for purposes other than encoding the displayed color information -- for double buffering, for Z buffering, and for pixmap storage.