# MVME1X2P4 VME Embedded Controller

# Programmer's Reference Guide

V1X2P4A/PG2

Edition of November 2000

### © Copyright 2000 Motorola, Inc.

### All rights reserved.

### Printed in the United States of America.

$\mathsf{Motorola}^{\circledR}$  and the Motorola logo are registered trademarks of Motorola, Inc.

MC68040<sup>TM</sup> and MC68060<sup>TM</sup> are trademarks of Motorola, Inc.

IndustryPack<sup>TM</sup> and IP<sup>TM</sup> are trademarks of GreenSpring Computers, Inc.

All other products mentioned in this document are trademarks or registered trademarks of their respective holders.

### **Safety Summary**

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual could result in personal injury or damage to the equipment.

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

#### Ground the Instrument.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. If the equipment is supplied with a three-conductor AC power cable, the power cable must be plugged into an approved three-contact electrical outlet, with the grounding wire (green/yellow) reliably connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards and local electrical regulatory codes.

### Do Not Operate in an Explosive Atmosphere.

Do not operate the equipment in any explosive atmosphere such as in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment could result in an explosion and cause injury or damage.

### **Keep Away From Live Circuits Inside the Equipment.**

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified service personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Service personnel should not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, such personnel should always disconnect power and discharge circuits before touching components.

### Use Caution When Exposing or Handling a CRT.

Breakage of a Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, do not handle the CRT and avoid rough handling or jarring of the equipment. Handling of a CRT should be done only by qualified service personnel using approved safety mask and gloves.

### Do Not Substitute Parts or Modify Equipment.

Do not install substitute parts or perform any unauthorized modification of the equipment. Contact your local Motorola representative for service and repair to ensure that all safety features are maintained.

### **Observe Warnings in Manual.**

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

To prevent serious injury or death from dangerous voltages, use extreme caution when handling, testing, and adjusting this equipment and its components.

### **Flammability**

All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers.

### **EMI Caution**

This equipment generates, uses and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection.

### **Lithium Battery Caution**

This product contains a lithium battery to power the clock and calendar circuitry.

Danger of explosion if battery is replaced incorrectly. Replace battery only with the same or equivalent type recommended by the equipment manufacturer. Dispose of used batteries according to the manufacturer's instructions.

Il y a danger d'explosion s'il y a remplacement incorrect de la batterie. Remplacer uniquement avec une batterie du même type ou d'un type équivalent recommandé par le constructeur. Mettre au rebut les batteries usagées conformément aux instructions du fabricant.

Explosionsgefahr bei unsachgemäßem Austausch der Batterie. Ersatz nur durch denselben oder einen vom Hersteller empfohlenen Typ. Entsorgung gebrauchter Batterien nach Angaben des Herstellers.

### **CE Notice (European Community)**

Motorola Computer Group products with the CE marking comply with the EMC Directive (89/336/EEC). Compliance with this directive implies conformity to the following European Norms:

EN55022 "Limits and Methods of Measurement of Radio Interference Characteristics of Information Technology Equipment"; this product tested to Equipment Class B

EN50082-1:1997 "Electromagnetic Compatibility—Generic Immunity Standard, Part 1. Residential, Commercial and Light Industry"

System products also fulfill EN60950 (product safety) which is essentially the requirement for the Low Voltage Directive (73/23/EEC).

Board products are tested in a representative system to show compliance with the above mentioned requirements. A proper installation in a CE-marked system will maintain the required EMC/safety performance.

In accordance with European Community directives, a "Declaration of Conformity" has been made and is on file within the European Union. The "Declaration of Conformity" is available on request. Please contact your sales representative.

### Notice

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to the Motorola Computer Group website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise altered without the permission of Motorola, Inc.

It is possible that this publication may contain reference to or information about Motorola products (machines and programs), programming, or services that are not available in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

### **Limited and Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and Documentation clause at DFARS 252.227-7014 (Jun. 1995).

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282

# **Contents**

| About This Manual                                   |       |

|-----------------------------------------------------|-------|

| Summary of Changes                                  | xxii  |

| Overview of Contents                                |       |

| Comments and Suggestions                            | xxiii |

| Conventions Used in This Manual                     |       |

| CHAPTER 1 Board Description and Memory Maps         |       |

| Introduction                                        | 1-1   |

| Overview                                            | 1-2   |

| The Petra ASIC and Second-Generation MVME1X2 Boards | 1-2   |

| I/O Routing                                         |       |

| VMEbus Interface                                    |       |

| Petra ASIC                                          | 1-5   |

| Applicable Industry Standards                       | 1-7   |

| Block Diagram                                       | 1-7   |

| Functional Description                              | 1-9   |

| VMEbus Interface and VMEchip2                       | 1-9   |

| Memory Maps                                         | 1-11  |

| Local Bus Memory Map                                | 1-11  |

| Normal Address Range                                | 1-11  |

| Detailed I/O Memory Maps                            | 1-17  |

| BBRAM/TOD Clock Memory Map                          | 1-33  |

| Interrupt Acknowledge Map                           | 1-39  |

| VMEbus Memory Map                                   |       |

| VMEbus Accesses to the Local Bus                    |       |

| VMEbus Short I/O Memory Map                         |       |

| Software Support Considerations                     |       |

| Interrupts                                          | 1-40  |

| Cache Coherency                                     | 1-41  |

| Sources of Local BERR*                              | 1-41  |

| Local Bus Time-Out                                  |       |

| VMEbus Access Time-Out                              |       |

| VMEbus BERR*                                        |       |

| Local DRAM Parity Error                             | 1-42  |

| VMEchip2                                                                                                                                                                                                                                                                                                                                                  | 1-42              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Bus Error Processing                                                                                                                                                                                                                                                                                                                                      | 1-43              |

| Description of Error Conditions on the MVME1X2P4                                                                                                                                                                                                                                                                                                          | 1-43              |

| MPU Parity Error                                                                                                                                                                                                                                                                                                                                          |                   |

| MPU Offboard Error                                                                                                                                                                                                                                                                                                                                        |                   |

| MPU TEA - Cause Unidentified                                                                                                                                                                                                                                                                                                                              | 1-44              |

| MPU Local Bus Timeout                                                                                                                                                                                                                                                                                                                                     | 1-44              |

| DMAC VMEbus Error                                                                                                                                                                                                                                                                                                                                         | 1-45              |

| DMAC Parity Error                                                                                                                                                                                                                                                                                                                                         | 1-45              |

| DMAC Offboard Error                                                                                                                                                                                                                                                                                                                                       | 1-46              |

| DMAC LTO Error                                                                                                                                                                                                                                                                                                                                            |                   |

| DMAC TEA - Cause Unidentified                                                                                                                                                                                                                                                                                                                             | 1-47              |

| LAN Parity Error                                                                                                                                                                                                                                                                                                                                          | 1-47              |

| LAN Offboard Error                                                                                                                                                                                                                                                                                                                                        |                   |

| LAN LTO Error                                                                                                                                                                                                                                                                                                                                             | 1-48              |

| SCSI Parity Error                                                                                                                                                                                                                                                                                                                                         | 1-49              |

| SCSI Offboard Error                                                                                                                                                                                                                                                                                                                                       | 1-49              |

| SCSI LTO Error                                                                                                                                                                                                                                                                                                                                            |                   |

| Proper Use of Bus Timers                                                                                                                                                                                                                                                                                                                                  |                   |

| MVME1X2P4 MC680x0 Indivisible Cycles                                                                                                                                                                                                                                                                                                                      |                   |

| Illegal Access to IP Modules from External VMEbus Masters .                                                                                                                                                                                                                                                                                               | 1-52              |

|                                                                                                                                                                                                                                                                                                                                                           |                   |

|                                                                                                                                                                                                                                                                                                                                                           |                   |

| CHAPTER 2 VMEchip2                                                                                                                                                                                                                                                                                                                                        |                   |

| ·                                                                                                                                                                                                                                                                                                                                                         | 2.1               |

| Introduction                                                                                                                                                                                                                                                                                                                                              |                   |

| Introduction                                                                                                                                                                                                                                                                                                                                              | 2-4               |

| Introduction                                                                                                                                                                                                                                                                                                                                              | 2-4<br>2-4        |

| Introduction                                                                                                                                                                                                                                                                                                                                              | 2-4<br>2-4<br>2-7 |

| Introduction                                                                                                                                                                                                                                                                                                                                              | 2-4<br>2-7<br>2-9 |

| Introduction                                                                                                                                                                                                                                                                                                                                              |                   |

| Introduction Functional Blocks Local-Bus-to-VMEbus Interface Local-Bus-to-VMEbus Requester VMEbus-to-Local-Bus Interface Local-Bus-to-VMEbus DMA Controller No-Address-Increment DMA Transfers                                                                                                                                                            |                   |

| Introduction Functional Blocks Local-Bus-to-VMEbus Interface Local-Bus-to-VMEbus Requester VMEbus-to-Local-Bus Interface Local-Bus-to-VMEbus DMA Controller No-Address-Increment DMA Transfers DMAC VMEbus Requester                                                                                                                                      |                   |

| Introduction Functional Blocks Local-Bus-to-VMEbus Interface Local-Bus-to-VMEbus Requester VMEbus-to-Local-Bus Interface Local-Bus-to-VMEbus DMA Controller No-Address-Increment DMA Transfers DMAC VMEbus Requester Tick and Watchdog Timers                                                                                                             |                   |

| Introduction Functional Blocks  Local-Bus-to-VMEbus Interface  Local-Bus-to-VMEbus Requester  VMEbus-to-Local-Bus Interface  Local-Bus-to-VMEbus DMA Controller  No-Address-Increment DMA Transfers  DMAC VMEbus Requester  Tick and Watchdog Timers  Prescaler                                                                                           |                   |

| Introduction Functional Blocks  Local-Bus-to-VMEbus Interface  Local-Bus-to-VMEbus Requester  VMEbus-to-Local-Bus Interface  Local-Bus-to-VMEbus DMA Controller  No-Address-Increment DMA Transfers  DMAC VMEbus Requester  Tick and Watchdog Timers  Prescaler  Tick Timers                                                                              |                   |

| Introduction Functional Blocks  Local-Bus-to-VMEbus Interface  Local-Bus-to-VMEbus Requester  VMEbus-to-Local-Bus Interface  Local-Bus-to-VMEbus DMA Controller  No-Address-Increment DMA Transfers  DMAC VMEbus Requester  Tick and Watchdog Timers  Prescaler  Tick Timers  Watchdog Timer                                                              |                   |

| Introduction Functional Blocks  Local-Bus-to-VMEbus Interface  Local-Bus-to-VMEbus Requester  VMEbus-to-Local-Bus Interface  Local-Bus-to-VMEbus DMA Controller  No-Address-Increment DMA Transfers  DMAC VMEbus Requester  Tick and Watchdog Timers  Prescaler  Tick Timers  Watchdog Timer  VMEbus Interrupter                                          |                   |

| Introduction Functional Blocks  Local-Bus-to-VMEbus Interface  Local-Bus-to-VMEbus Requester  VMEbus-to-Local-Bus Interface  Local-Bus-to-VMEbus DMA Controller  No-Address-Increment DMA Transfers  DMAC VMEbus Requester  Tick and Watchdog Timers  Prescaler  Tick Timers  Watchdog Timer  VMEbus Interrupter  VMEbus System Controller                |                   |

| Introduction Functional Blocks  Local-Bus-to-VMEbus Interface  Local-Bus-to-VMEbus Requester  VMEbus-to-Local-Bus Interface  Local-Bus-to-VMEbus DMA Controller  No-Address-Increment DMA Transfers  DMAC VMEbus Requester  Tick and Watchdog Timers.  Prescaler  Tick Timers  Watchdog Timer  VMEbus Interrupter  VMEbus System Controller  Arbiter      |                   |

| Introduction Functional Blocks  Local-Bus-to-VMEbus Interface  Local-Bus-to-VMEbus Requester  VMEbus-to-Local-Bus Interface  Local-Bus-to-VMEbus DMA Controller  No-Address-Increment DMA Transfers  DMAC VMEbus Requester  Tick and Watchdog Timers  Prescaler  Tick Timers  Watchdog Timer.  VMEbus System Controller  Arbiter  IACK Daisy-Chain Driver |                   |

| Introduction Functional Blocks  Local-Bus-to-VMEbus Interface  Local-Bus-to-VMEbus Requester  VMEbus-to-Local-Bus Interface  Local-Bus-to-VMEbus DMA Controller  No-Address-Increment DMA Transfers  DMAC VMEbus Requester  Tick and Watchdog Timers.  Prescaler  Tick Timers  Watchdog Timer  VMEbus Interrupter  VMEbus System Controller  Arbiter      |                   |

| Local Bus Interrupter and Interrupt Handler                 |      |

|-------------------------------------------------------------|------|

| Global Control and Status Registers                         | 2-20 |

| LCSR Programming Model                                      | 2-20 |

| Programming the VMEbus Slave Map Decoders                   | 2-26 |

| VMEbus Slave Ending Address Register 1                      | 2-28 |

| VMEbus Slave Starting Address Register 1                    | 2-28 |

| VMEbus Slave Ending Address Register 2                      |      |

| VMEbus Slave Starting Address Register 2                    | 2-29 |

| VMEbus Slave Address Translation Address Offset Register 1  | 2-29 |

| VMEbus Slave Address Translation Select Register 1          |      |

| VMEbus Slave Address Translation Address Offset Register 2  | 2-31 |

| VMEbus Slave Address Translation Select Register 2          |      |

| VMEbus Slave Write Post / Snoop Control Register 2          | 2-32 |

| VMEbus Slave Address Modifier Select Register 2             |      |

| VMEbus Slave Write Post and Snoop Control Register 1        |      |

| VMEbus Slave Address Modifier Select Register 1             |      |

| Programming the Local-Bus-to-VMEbus Map Decoders            |      |

| Local Bus Slave (VMEbus Master) Ending Address Register 1   |      |

| Local Bus Slave (VMEbus Master) Starting Address Register 1 |      |

| Local Bus Slave (VMEbus Master) Ending Address Register 2   |      |

| Local Bus Slave (VMEbus Master) Starting Address Register 2 |      |

| Local Bus Slave (VMEbus Master) Ending Address Register 3   |      |

| Local Bus Slave (VMEbus Master) Starting Address Register 3 |      |

| Local Bus Slave (VMEbus Master) Ending Address Register 4   |      |

| Local Bus Slave (VMEbus Master) Starting Address Register 4 | 2-42 |

| Local Bus Slave (VMEbus Master)                             |      |

| Address Translation Address Register 4                      | 2-42 |

| Local Bus Slave (VMEbus Master)                             |      |

| Address Translation Select Register 4                       |      |

| Local Bus Slave (VMEbus Master) Attribute Register 4        |      |

| Local Bus Slave (VMEbus Master) Attribute Register 3        |      |

| Local Bus Slave (VMEbus Master) Attribute Register 2        |      |

| Local Bus Slave (VMEbus Master) Attribute Register 1        |      |

| VMEbus Slave GCSR Group Address Register                    |      |

| VMEbus Slave GCSR Board Address Register                    |      |

| Local-Bus-to-VMEbus Enable Control Register                 |      |

| Local-Bus-to-VMEbus I/O Control Register                    |      |

| ROM Control Register                                        |      |

| Programming the VMEchip2 DMA Controller                     |      |

| DMAC Registers                                              |      |

| EPROM Decoder, SRAM and DMA Control Register                |      |

| Local-Bus-to-VMEbus Requester Control Register              | 2-54 |

| DMAC Control Register 1 (bits 0-7)                            | 2-55 |

|---------------------------------------------------------------|------|

| DMAC Control Register 2 (bits 8-15)                           | 2-57 |

| DMAC Control Register 2 (bits 0-7)                            |      |

| DMAC Local Bus Address Counter                                |      |

| DMAC VMEbus Address Counter                                   | 2-60 |

| DMAC Byte Counter                                             | 2-60 |

| Table Address Counter                                         | 2-60 |

| VMEbus Interrupter Control Register                           | 2-61 |

| VMEbus Interrupter Vector Register                            | 2-62 |

| MPU Status and DMA Interrupt Count Register                   |      |

| DMAC Status Register                                          |      |

| Programming the Tick and Watchdog Timers                      | 2-64 |

| VMEbus Arbiter Time-Out Control Register                      |      |

| DMAC Ton/Toff Timers and                                      |      |

| VMEbus Global Time-out Control Register                       | 2-65 |

| VME Access, Local Bus, and Watchdog Time-out Control Register |      |

| Prescaler Control Register                                    |      |

| Tick Timer 1 Compare Register                                 | 2-68 |

| Tick Timer 1 Counter                                          | 2-68 |

| Tick Timer 2 Compare Register                                 | 2-69 |

| Tick Timer 2 Counter                                          | 2-69 |

| Board Control Register                                        | 2-70 |

| Watchdog Timer Control Register                               | 2-71 |

| Tick Timer 2 Control Register                                 |      |

| Tick Timer 1 Control Register                                 |      |

| Prescaler Counter                                             | 2-73 |

| Programming the Local Bus Interrupter                         | 2-74 |

| Local Bus Interrupter Status Register (bits 24-31)            | 2-77 |

| Local Bus Interrupter Status Register (bits 16-23)            | 2-78 |

| Local Bus Interrupter Status Register (bits 8-15)             | 2-79 |

| Local Bus Interrupter Status Register (bits 0-7)              | 2-80 |

| Local Bus Interrupter Enable Register (bits 24-31)            | 2-81 |

| Local Bus Interrupter Enable Register (bits 16-23)            | 2-82 |

| Local Bus Interrupter Enable Register (bits 8-15)             |      |

| Local Bus Interrupter Enable Register (bits 0-7)              | 2-84 |

| Software Interrupt Set Register (bits 8-15)                   |      |

| Interrupt Clear Register (bits 24-31)                         | 2-85 |

| Interrupt Clear Register (bits 16-23)                         | 2-86 |

| Interrupt Clear Register (bits 8-15)                          |      |

| Interrupt Level Register 1 (bits 24-31)                       | 2-87 |

| Interrupt Level Register 1 (bits 16-23)                       | 2-88 |

| Interrupt Level Register 1 (bits 8-15)                        | 2-88 |

| Interrupt Level Register 1 (bits 0-7)   | 2-89  |

|-----------------------------------------|-------|

| Interrupt Level Register 2 (bits 24-31) |       |

| Interrupt Level Register 2 (bits 16-23) |       |

| Interrupt Level Register 2 (bits 8-15)  | 2-90  |

| Interrupt Level Register 2 (bits 0-7)   | 2-91  |

| Interrupt Level Register 3 (bits 24-31) | 2-91  |

| Interrupt Level Register 3 (bits 16-23) | 2-92  |

| Interrupt Level Register 3 (bits 8-15)  | 2-92  |

| Interrupt Level Register 3 (bits 0-7)   | 2-93  |

| Interrupt Level Register 4 (bits 24-31) | 2-93  |

| Interrupt Level Register 4 (bits 16-23) |       |

| Interrupt Level Register 4 (bits 8-15)  |       |

| Interrupt Level Register 4 (bits 0-7)   |       |

| Vector Base Register                    | 2-95  |

| I/O Control Register 1                  |       |

| I/O Control Register 2                  |       |

| I/O Control Register 3                  |       |

| Miscellaneous Control Register          |       |

| GCSR Programming Model                  | 2-100 |

| Programming the GCSR                    | 2-102 |

| VMEchip2 Revision Register              | 2-103 |

| VMEchip2 ID Register                    | 2-104 |

| VMEchip2 LM/SIG Register                |       |

| VMEchip2 Board Status/Control Register  |       |

| General Purpose Register 0              | 2-107 |

| General Purpose Register 1              |       |

| General Purpose Register 2              |       |

| General Purpose Register 3              |       |

| General Purpose Register 4              |       |

| General Purpose Register 5              | 2-108 |

| CHAPTER 3 MC2 Functions                 |       |

|                                         |       |

| Introduction                            |       |

| Summary of Major Features               |       |

| Functional Description                  |       |

| Petra/MC2 Chip Initialization           |       |

| Flash and EPROM Interface               |       |

| BBRAM Interface                         |       |

| 82596CA LAN Interface                   |       |

| MPU Port and MPU Channel Attention      | 3-3   |

| MC680x0-Bus Master Support for 82596CA           | 3-4    |

|--------------------------------------------------|--------|

| LANC Bus Error                                   |        |

| LANC Interrupt                                   | 3-5    |

| 53C710 SCSI Controller Interface                 | 3-5    |

| SRAM Memory Controller                           | 3-5    |

| SDRAM Memory Controller                          |        |

| Z85230 SCC Interface                             | 3-7    |

| Tick Timers.                                     | 3-8    |

| Watchdog Timer                                   | 3-9    |

| Local Bus Timer                                  |        |

| Petra/MC2 Registers: Memory Map                  | . 3-10 |

| Programming Model                                | . 3-11 |

| MC2 Sector ID Register                           |        |

| MC2 Sector Revision Register                     |        |

| General Control Register                         | . 3-12 |

| Interrupt Vector Base Register                   |        |

| Programming the Tick Timers                      | . 3-15 |

| Tick Timer 1 and 2 Compare and Counter Registers | . 3-15 |

| LSB Prescaler Count Register                     | .3-17  |

| Prescaler Clock Adjust Register                  | . 3-17 |

| Tick Timer 1 and 2 Control Registers             | . 3-18 |

| Tick Timer Interrupt Control Registers           | .3-19  |

| DRAM Parity Error Interrupt Control Register     | . 3-21 |

| SCC Interrupt Control Register                   | . 3-22 |

| Tick Timer 3 and 4 Control Registers             | . 3-23 |

| DRAM and SRAM Memory Controller Registers        | . 3-24 |

| DRAM Space Base Address Register                 |        |

| SRAM Space Base Address Register                 |        |

| DRAM Space Size Register                         | . 3-25 |

| DRAM/SRAM Options Register                       |        |

| SRAM Space Size Register                         | . 3-28 |

| LANC Error Status Register                       |        |

| 82596CA LANC Interrupt Control Register          |        |

| LANC Bus Error Interrupt Control Register        |        |

| SCSI Error Status Register                       |        |

| General-Purpose Inputs Register                  |        |

| MVME1X2P4 Version Register                       |        |

| SCSI Interrupt Control Register                  |        |

| Tick Timer 3 and 4 Compare and Counter Registers |        |

| Bus Clock Register                               |        |

| EPROM Access Time Control Register               |        |

| Flash Access Time Control Register               | . 3-39 |

| ABORT Switch Interrupt Control Register                       | 3-40 |

|---------------------------------------------------------------|------|

| RESET Switch Control Register                                 |      |

| Watchdog Timer Control Register                               | 3-42 |

| Access and Watchdog Time Base Select Register                 | 3-43 |

| DRAM Control Register                                         | 3-44 |

| MPU Status Register                                           | 3-46 |

| 32-bit Prescaler Count Register                               | 3-47 |

|                                                               |      |

| CHAPTER 4 IP2 Functions                                       |      |

| Introduction                                                  | 4-1  |

| Summary of Major Features                                     | 4-1  |

| IP2/IP1 Bug Fixes                                             |      |

| Command Chain Table Update                                    | 4-2  |

| DMA End                                                       | 4-2  |

| IP Bus Reset Compatibility                                    | 4-3  |

| Functional Description                                        | 4-3  |

| General Description                                           | 4-3  |

| Cache Coherency                                               | 4-4  |

| Local Bus to IndustryPack DMA Controllers                     | 4-4  |

| Clocking Environments and Performance                         | 4-6  |

| Programmable Clock                                            | 4-8  |

| Error Reporting                                               | 4-8  |

| Error Reporting as a Local Bus Slave                          | 4-8  |

| Error Reporting as a Local Bus Master                         |      |

| IndustryPack Error Reporting                                  | 4-9  |

| Interrupts                                                    | 4-9  |

| Overall Memory Map                                            | 4-10 |

| Programming Model                                             | 4-11 |

| Chip ID Register                                              | 4-18 |

| Chip Revision Register                                        | 4-18 |

| Vector Base Register                                          |      |

| Memory Base Address Registers: IP_a, IP_b, IP_c, IP_d         |      |

| IP_a or Double-Size IP_ab Memory Base Address Registers       |      |

| IP_b Memory Base Address Registers                            |      |

| IP_c or Double-Size IP_cd Memory Base Address Registers       |      |

| IP_d Memory Base Address Registers                            |      |

| Memory Size Registers: IP_a, IP_b, IP_c, IP_d                 |      |

| IRQ0/IRQ1 Interrupt Control Registers: IP_a, IP_b, IP_c, IP_d |      |

| General Control Registers: IP_a, IP_b, IP_c, IP_d             |      |

| IP Clock Register                                             | 4-28 |

| DMA Arbitration Control Register               | 4-29 |

|------------------------------------------------|------|

| IP RESET Register                              |      |

| Programming the DMA Controllers                |      |

| DMA Enable Function                            |      |

| DMA Control and Status Register Set Definition | 4-34 |

| Programming the Programmable Clock             |      |

| Local Bus to IndustryPack Addressing           |      |

| Eight-Bit Memory Space                         | 4-50 |

| 16-Bit Memory Space                            |      |

| 32-Bit Memory Space                            | 4-52 |

| IP_a I/O Space                                 | 4-53 |

| IP_ab I/O Space                                | 4-54 |

| IP_a ID Space                                  | 4-55 |

| IP to Local Bus Data Routing                   | 4-56 |

| Memory Space Accesses                          | 4-56 |

| I/O and ID Space Accesses                      | 4-58 |

|                                                |      |

| CHAPTER 5 MCECC Functions                      |      |

| Introduction                                   | 5.1  |

| Features                                       |      |

|                                                |      |

| Functional Description                         |      |

| General Description                            |      |

| Performance.                                   |      |

| Cache Coherency                                |      |

| ECC                                            |      |

| Cycle Types                                    |      |

| Error Reporting Error Logging                  |      |

| Scrub                                          |      |

| Refresh                                        |      |

| Arbitration                                    |      |

| Chip Defaults                                  |      |

| Programming Model                              |      |

| Chip ID Register                               |      |

| Chip Revision Register                         |      |

| Memory Configuration Register                  |      |

| Base Address Register                          |      |

| DRAM Control Register                          |      |

| BCLK Frequency Register                        |      |

| Data Control Register                          |      |

| ····· - ×× Ø-× ·············                   |      |

| Scrub Control Register                     | 5-19 |

|--------------------------------------------|------|

| Scrub Period Register Bits 15-8            | 5-20 |

| Scrub Period Register Bits 7-0             | 5-20 |

| Chip Prescaler Counter                     | 5-21 |

| Scrub Time On/Time Off Register            | 5-21 |

| Scrub Prescaler Counter (Bits 21-16)       | 5-23 |

| Scrub Prescaler Counter (Bits 15-8)        | 5-23 |

| Scrub Prescaler Counter (Bits 7-0)         | 5-24 |

| Scrub Timer Counter (Bits 15-8)            |      |

| Scrub Timer Counter (Bits 7-0)             |      |

| Scrub Address Counter (Bits 26-24)         |      |

| Scrub Address Counter (Bits 23-16)         |      |

| Scrub Address Counter (Bits 15-8)          | 5-26 |

| Scrub Address Counter (Bits 7-4)           | 5-26 |

| Error Logger Register                      |      |

| Error Address (Bits 31-24)                 |      |

| Error Address (Bits 23-16)                 |      |

| Error Address Bits (15-8)                  |      |

| Error Address Bits (7-4)                   |      |

| Error Syndrome Register                    |      |

| Defaults Register 1                        |      |

| Defaults Register 2                        |      |

| SDRAM Configuration Register               |      |

| Initialization                             |      |

| Syndrome Decoding                          | 5-36 |

| APPENDIX A Summary of Changes              |      |

| Introduction                               | A-1  |

| APPENDIX B Using Interrupts on the MVME1X2 | P4   |

| Example: Tick Timer 1 Periodic Interrupt   | B-1  |

| APPENDIX C Related Documentation           |      |

| Motorola Computer Group Documents          | C-1  |

| Manufacturers' Documents                   |      |

| Related Specifications                     |      |

| • • • • • • • • • • • • • • • • • • •      |      |

# **List of Figures**

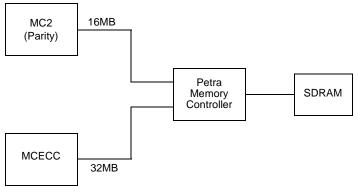

| Figure 1-1. MVME1X2P4 Memory Control Options | .1-4 |

|----------------------------------------------|------|

| Figure 1-2. MVME1X2P4 Block Diagram          | .1-8 |

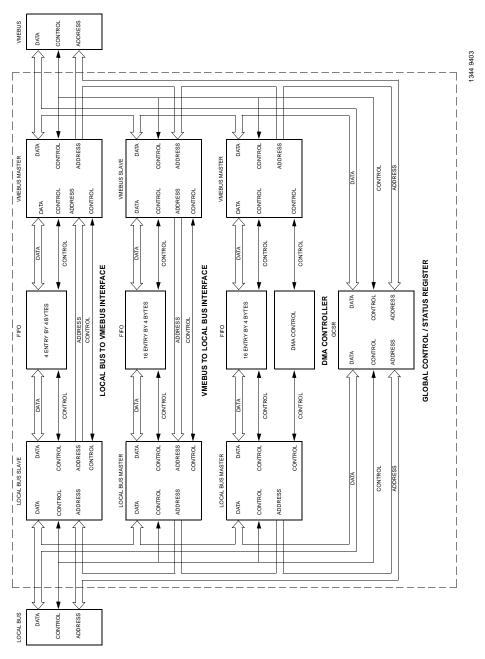

| Figure 2-1. VMEchip2 Block Diagram           | .2-5 |

# **List of Tables**

| Table 1-1. MVME1X2P4 Features Summary                           | 1-6   |

|-----------------------------------------------------------------|-------|

| Table 1-2. Functions Duplicated in VMEchip2 and Petra ASICs     | 1-10  |

| Table 1-3. MVME1X2P4 Local Bus Memory Map                       | 1-12  |

| Table 1-4. MVME1X2P4 Local I/O Devices Memory Map               | 1-14  |

| Table 1-5. VMEchip2 Memory Map (Sheet 1 of 3)                   | 1-18  |

| Table 1-6. Petra MC2 Functions: Register Map                    | 1-23  |

| Table 1-7. Petra IP2 Functions: Overall Memory Map              | 1-24  |

| Table 1-8. Petra IP2 Memory Map — Control/Status Registers      | 1-25  |

| Table 1-9. Z85230 SCC Register Addresses                        | 1-31  |

| Table 1-10. 82596CA Ethernet LAN Memory Map                     | 1-31  |

| Table 1-11. 53C710 SCSI Memory Map                              | 1-32  |

| Table 1-12. M48T58 BBRAM/TOD Clock Memory Map                   | 1-33  |

| Table 1-13. BBRAM Configuration Area Memory Map                 | 1-34  |

| Table 1-14. TOD Clock Memory Map                                | 1-35  |

| Table 2-1. Features of the VMEchip2 ASIC                        | 2-1   |

| Table 2-2. VMEchip2 Memory Map—LCSR Summary (Sheet 1 of 2)      | 2-22  |

| Table 2-3. DMAC Command Packet Format                           | 2-53  |

| Table 2-4. Local Bus Interrupter Summary                        | 2-75  |

| Table 2-5. VMEchip2 Memory Map (GCSR Summary)                   | 2-103 |

| Table 3-1. MC2 Functions on the Petra ASIC                      | 3-1   |

| Table 3-2. SDRAM Performance                                    | 3-7   |

| Table 3-3. SCC Device Addressing                                | 3-8   |

| Table 3-4. Petra MC2 Functions: Register Map                    | 3-10  |

| Table 3-5. Interrupt Vector Base Register Encoding and Priority | 3-14  |

| Table 3-6. DRAM Size Control Bit Encoding                       | 3-26  |

| Table 3-7. DRAM Size Control Bit Encoding                       | 3-27  |

| Table 3-8. SRAM Size Control Bit Encoding                       | 3-28  |

| Table 3-9. SRAM Size Control Bit Encoding                       | 3-29  |

| Table 4-1. IP2 Functions on the Petra ASIC                      | 4-1   |

| Table 4-2. IP2 sector Clock Cycles                              | 4-7   |

| Table 4-3. IP2 Sector Overall Memory Map                        | 4-10  |

| Table 4-4. Petra IP2 Memory Map — Control/Status Registers      | 4-12  |

| Table 5-1. MCECC Functions on the Petra ASIC                    | 5-2   |

| Table 5-2. Memory System Cycle Timing                           | 5-4   |

| Table 5-3. MCECC Sector Internal Register Memory Map | 5-11 |

|------------------------------------------------------|------|

| Table 5-4. Syndrome Bit Encoding                     | 5-36 |

| Table 5-5. Identifying SDRAM Bank in Error           | 5-37 |

| Table A-1. List of Changes                           | A-1  |

| Table C-1. Motorola Computer Group Documents         | C-1  |

| Table C-2. Manufacturers' Documents                  |      |

| Table C-3. Related Specifications                    | C-3  |

# **About This Manual**

This manual provides board-level information and detailed ASIC information, including register bit descriptions, for the MVME162P-244 and -344 as well as the MVME172P-644 series of embedded controllers, known collectively as the "MVME1X2P4" because they are equipped with the "Petra" chip and accommodate up to four IP modules.

The "Petra" chip that distinguishes MVME1X2P4 embedded controllers is an application-specific integrated circuit (ASIC) which combines the functions previously covered by the MC2 chip, the IP2 chip, and the MCECC chip in a single ASIC. As of the publication date, the information presented in this manual applies to the following MVME1X2P4 models:

| Model Number    | Characteristics                                           |

|-----------------|-----------------------------------------------------------|

| MVME162P-244L   | 25MHz 68LC040, 16MB SDRAM, 2 SIO, 4 DMA IP                |

| MVME162P-244LE  | 25MHz 68LC040, 16MB SDRAM, 2 SIO, 4 DMA IP, Ethernet      |

| MVME162P-244LSE | 25MHz 68LC040, 16MB SDRAM, 2 SIO, 4 DMA IP, SCSI/Ethernet |

| MVME162P-344    | 32MHz 68040, 16MB SDRAM, 2 SIO, 4 DMA IP                  |

| MVME162P-344S   | 32MHz 68040, 16MB SDRAM, 2 SIO, 4 DMA IP, SCSI            |

| MVME162P-344E   | 32MHz 68040, 16MB SDRAM, 2 SIO, 4 DMA IP, Ethernet        |

| MVME162P-344SE  | 32MHz 68040, 16MB SDRAM, 2 SIO, 4 DMA IP, SCSI/Ethernet   |

| MVME172P-644L   | 64MHz 68LC060, 16MB SDRAM, 2 SIO, 4 DMA IP                |

| MVME172P-644LE  | 64MHz 68LC060, 16MB SDRAM, 2 SIO, 4 DMA IP, Ethernet      |

| MVME172P-644LSE | 60MHz 68060, 16MB SDRAM, 2 SIO, 4 DMA IP, SCSI/Ethernet   |

If the part number of your board includes a "PA" (for example: MVME162PA-244L), your board is equipped with a second-generation Petra ASIC. All other particulars of the board remain the same.

This manual is intended for anyone who designs OEM systems, adds capability to an existing compatible system, or works in a lab environment for experimental purposes. A basic knowledge of computers and digital logic is assumed. To use this manual, you may also wish to become familiar with the publications listed in Appendix C, *Related Documentation*.

# **Summary of Changes**

This is the second edition of the *Programmer's Reference Guide*. It supersedes the July 2000 edition and incorporates the following updates.

| Date         | Description of Change                                                                                                                                                                                                   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| October 2000 | The part number of the manual was changed from V1X2PFXA/PG1 to V1X2P4A/PG1 to better reflect board nomenclature.                                                                                                        |

| October 2000 | Descriptions of the snoop function on boards equipped with the MC68060 processor (as described on page 2-32, for example) have been updated.                                                                            |

| October 2000 | References to IP2 and MC2 revision levels at various points in the text (in Chapter 3 under <i>MC2 Sector Revision Register</i> , for example) were incremented from 02 to 03 to reflect this change in the Petra chip. |

| October 2000 | References in Chapter 4 to an irregularity in the behavior of the DMA "halt" function across DMA channels A, B, C, and D (as described on page 4-32, for example) were dropped, as this anomaly has been corrected.     |

# **Overview of Contents**

Chapter 1, *Board Description and Memory Maps*, describes the board-level hardware features of MVME1X2P4 single-board computers. It includes memory maps and a discussion of some general software considerations such as cache coherency, interrupts, and bus errors.

Chapter 2, *VMEchip2*, describes the VMEchip2 ASIC, the local bus/VMEbus interface chip on MVME1X2P4 boards.

Chapter 3, *MC2 Functions*, describes MC2 functionality as implemented in the Petra ASIC. The MC2 Memory Controller ASIC is one of three ASICs (the MC2 chip, the IP2 chip, and the MCECC chip) used on earlier MVME162/172 models whose functions are now incorporated into the Petra chip on the MVME1X2P4.

Chapter 4, *IP2 Functions*, describes IP2 functionality as implemented in the Petra ASIC. The IP2 IndustryPack Interface Controller ASIC is the second of three ASICs used on earlier MVME162/172 models whose functions are now incorporated into the Petra chip on the MVME1X2P4.

Chapter 5, *MCECC Functions*, describes MCECC functionality as implemented in the Petra ASIC. The ECC DRAM Controller ASIC (MCECC) is the third of three ASICs used on earlier MVME162/172 models whose functions are now incorporated into the Petra chip on the MVME1X2P4.

Appendix A, *Summary of Changes*, lists the modifications that accompanied the introduction of the Petra ASIC on the MVME162P4 and MVME172P4.

Appendix B, *Using Interrupts on the MVME1X2P4*, illustrates an approach to generating and handling a VMEchip2 tick timer interrupt on an MVME1X2P4 that has a VMEbus connection.

Appendix C, *Related Documentation*, lists all documentation related to the MVME162P4 and MVME172P4.

# **Comments and Suggestions**

Motorola welcomes and appreciates your comments on its documentation. We want to know what you think about our manuals and how we can make them better. Mail comments to:

Motorola Computer Group Reader Comments DW164 2900 S. Diablo Way Tempe, Arizona 85282

You can also submit comments to the following e-mail address: reader-comments@mcg.mot.com

In all your correspondence, please list your name, position, and company. Be sure to include the title and part number of the manual and tell how you used it. Then tell us your feelings about its strengths and weaknesses and any recommendations for improvements.

# **Conventions Used in This Manual**

The following typographical conventions are used in this document:

\$ dollar specifies a hexadecimal number

% percent specifies a binary number

& ampersand specifies a decimal number

Unless otherwise specified, all address references are in hexadecimal.

An asterisk (\*) following the signal name for signals which are level significant denotes that the signal is true or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are edge significant denotes that the actions initiated by that signal occur on high to low transition

#### bold

is used for user input that you type just as it appears; it is also used for commands, options and arguments to commands, and names of programs, directories and files.

#### italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples, and to introduce new terms.

#### courier

is used for system output (for example, screen displays, reports), examples, and system prompts.

#### <Enter>, <Return> or <CR>

represent the carriage return or Enter key.

#### **CTRL**

represents the Control key. Execute control characters by pressing the Ctrl key and the letter simultaneously, for example, **Ctrl-d**.

In this manual, assertion and negation are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation and negate indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

Data and address sizes are defined as follows:

- □ A *byte* is eight bits, numbered 0 through 7, with bit 0 being the least significant.

- □ A *word* is 16 bits, numbered 0 through 15, with bit 0 being the least significant.

- □ A *longword* is 32 bits, numbered 0 through 31, with bit 0 being the least significant.

The terms *control bit, status bit, true*, and *false* are used extensively in this document. The term *control bit* is used to describe a bit in a register that can be set and cleared under software control. The term *true* is used to indicate that a bit is in the state that enables the function it controls. The term *false* is used to indicate that the bit is in the state that disables the function it controls. In all tables, the terms 0 and 1 are used to describe the actual value that should be written to the bit, or the value that it yields when read. The term *status bit* is used to describe a bit in a register that reflects a specific condition. The status bit can be read by software to determine operational or exception conditions.

# Introduction

This manual supplies programming information for the MVME162P4 and MVME172P4 Embedded Controllers, known collectively as the "MVME1X2P4". Extensive programming information is provided for the Application-Specific Integrated Circuit (ASIC) devices used on the board. Reference information is also included for the Large Scale Integration (LSI) devices used on the board and sources for additional information are provided as well.

This chapter briefly describes the board level hardware features of the MVME1X2P4 Embedded Controller. The chapter begins with a board-level overview and features list. Memory maps are next, and the chapter closes with some general software considerations such as cache coherency, interrupts, and bus errors. All programmable registers that reside in ASICs on the MVME1X2P4 are covered in the chapters devoted to those ASICs.

#### Note

The MVME1X2P4's new "Petra" ASIC combines the functions previously covered by the MC2 chip, the IP2 chip, and the MCECC chip in a single ASIC. For ease of use in conjunction with programming models and documentation developed for earlier boards, however, the structure of this manual preserves the functional distinctions that formerly characterized those three ASICs.

Chapter 2 describes the VMEchip2 ASIC. Chapters 3, 4, and 5 respectively cover MC2 chip functions, IP2 chip functions, and MCECC chip functions, all three of which are now implemented by the Petra ASIC. Appendix A describes the use of interrupts. Readers more interested in programmable register bit definitions than in hardware functionality may wish to focus on Chapters 2, 3, 4, and 5. The related background information found in Chapter 1 (this chapter) may be of use in some cases.

### **Overview**

The MVME162P4 is based on the MC68040 or MC68LC040 microprocessor. The MVME172P4 is based on the MC68060 or MC68LC060 microprocessor. The board artwork is otherwise the same for both MVME1X2P4 models.

Both models are available in various versions with the features listed in Table 1-1 on page 1-6. No-IP, no-SCSI, and no-LAN options are available as well.

### The Petra ASIC and Second-Generation MVME1X2 Boards

Due to rapid changes in technology, the production of certain ASICs used on first- and second-generation MVME162/172 series boards has ended. The discontinued ASICs are the MC, MC2, IPIC, IP2, and MCECC chips. The Petra chip was developed to replace these discontinued ASICs.

The Petra ASIC is functionally compatible with each of the components that it replaces. In cases where functionality between ASICs is exclusive, configuration switches or jumpers are provided to let you select the desired functionality. For instance, the MC and MC2 chips differed in their implementation of Flash write protection. Boards built with the Petra ASIC, accordingly, have a configuration switch so that you can determine which method to use.

In several areas of functionality, the configuration switches provide backward compatibility with earlier MVME162/172 implementations, but their settings can be overridden in software if desired. A "R/W" by the corresponding register table entry denotes instances where this capability is present.

Where the older technology supported "fast page" or "EDO" DRAM chips, the Petra memory controllers support SDRAM devices. The two memory controllers modeled in Petra duplicate the functionality of the "parity" memory controller found in the MC ASICs as well as that of the "single-bit error correcting/double-bit error detecting" memory controller found in the MCECC ASICs (see Figure 1-1).

In line with this flexibility in memory control, where previous MVME1X2LX-series (2IP) Programmer's Reference Guides documented only the "parity" memory controller model, this guide describes the "parity" model (in Chapter 3) as well as the MCECC model (in Chapter 5). You can enable the ECC function if you so desire.

There is logic to prevent you from using both SDRAM memory controllers at the same time. Regardless of which memory controller is enabled, the same SDRAM memory array is targeted. The SDRAM array is 32 data bits wide with 7 checkbits. The array architecture is a non-interleaved single bank for sizes below 32MB. For array sizes above 32MB, additional physical memory banks are added but the architecture remains non-interleaved. Since the 7 checkbits enable error detection and correction, the MC "parity memory controller" actually interfaces to an error-correcting memory array. In this case, a parity error is defined to be a multibit error that cannot be corrected. Memory scrubbing is not available with the "parity memory controller".

A final note on the SDRAM implementation: The bandwidth between the SDRAM and local bus is greater than it was with the earlier DRAM array. As a result, software takes less time to execute. Applications that incorporate elapsed-time functions which are dependent on code execution may have problems.

For readers who need to know the ASIC-specific differences between the MVME1X2P2 programming models in detail, certain areas of the text in this manual are printed in italics and marked with change bars (as is done here). Readers should compare those sections to the corresponding sections of the first-generation manuals.

## I/O Routing

Two DB25 front panel I/O connectors furnish the I/O connection for the serial ports. The balance of the I/O is routed to the VMEbus P2 connector. A P2 transition board and cables link the main board to a user-selected transition board.

Previous memory model (emulates parity memory) may be desirable for compatibility with existing implementations.

New memory model (has error correction circuitry) - may be desirable for the improved performance, or in applications where memory requirements exceed 16MB.

2610 9908

### Figure 1-1. MVME1X2P4 Memory Control Options

The MVME1X2P4 supports the MVME712M and MVME712B transition boards. It is also compatible with older, discontinued boards of the MVME712 series: MVME712-12, MVME712-13, MVME712A, or MVME712AM (all referred to in this manual collectively as MVME712x, unless separately specified). These transition boards provide configuration headers, serial port drivers, and industry-standard connectors for the I/O devices. Though originally designed to support MVME167 boards, the MVME712 series transition boards are compatible with the MVME1X2P4 as well. (Special precautions apply in a few cases. Refer to the section on the Serial Communications Interface in the MVME1X2P4 Installation and Use manual for more information.)

### **VMEbus Interface**

The VMEbus interface is implemented with an ASIC called the VMEchip2. The VMEchip2 includes:

- □ Two tick timers

- □ A watchdog timer

- Programmable map decoders for the master and slave interfaces

- □ A VMEbus to/from local bus DMA controller

- □ A VMEbus to/from local bus non-DMA programmed access interface

- □ A VMEbus interrupter, a VMEbus system controller, a VMEbus interrupt handler, and a VMEbus requester

Processor-to-VMEbus transfers can be D8, D16, or D32. VMEchip2 DMA transfers to the VMEbus, however, can be D16, D32, D16/BLT, D32/BLT, or D64/MBLT.

### Petra ASIC

The "Petra" ASIC combines the functions of the MC2 chip, the IP2 chip, and the MCECC chip in a single device.

Former MC2 chip functions now implemented by the Petra ASIC include four tick timers; the interfaces to the LAN chip, SCSI chip, serial port chip, and BBRAM; the programmable interface for the DRAM and/or SRAM; and Flash write enable.

Former IndustryPack Interface Controller (IP2 chip) functions now implemented by the Petra ASIC include control and status information, including DMA control, for up to two single-size IndustryPacks (IPs) or one double-size IP that can be plugged into the MVME1X2P4 main module.

The Petra ASIC also performs the memory control functions previously carried out by the MCECC chip Memory Controller ASIC: It supplies the programmable interface for the ECC-protected 16/32MB DRAM emulation.

The following table summarizes the features of the MVME162P4 and MVME172P4 Embedded Controllers.

Table 1-1. MVME1X2P4 Features Summary

| Feature                | MVME162P4                                                                                                                                                                                     | MVME172P4                                                                                |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|

| Processor              | 25/32MHz 32-bit MC68040 or<br>MC68LC040 microprocessor                                                                                                                                        | 60MHz 32-bit MC68060<br>microprocessor, or 64MHz 32-bit<br>MC68LC060 microprocessor      |  |

| DRAM                   | 16/32MB synchronous DRAM (SDRAM). Configurable to emulate 1/4/8/16MB parity-protected DRAM or 4/8/16/32MB ECC-protected DRAM  MVME1X2P4 boards use SDRAM (Synchronous DRAM) in place of DRAM. |                                                                                          |  |

| SRAM                   | 512KB SRAM with battery backup                                                                                                                                                                |                                                                                          |  |

| EPROM                  | One JEDEC standard 32-pin PLCC EPROM socket (EPROMs may be shipped separately)                                                                                                                |                                                                                          |  |

| Flash                  | One Intel 28F008SA 1Mx8 or<br>2Mx8 Flash memory device with<br>optional write protection                                                                                                      | One Intel 28F160S5 1Mx8 or 2Mx8<br>Flash memory device with optional<br>write protection |  |

| NVRAM and RTC          | 8K by 8 Non-Volatile RAM (NVRAM) and Real-Time Clock (RTC) with battery backup and watchdog function (SGS-Thomson M48T58)                                                                     |                                                                                          |  |

| Timers                 | Four 32-bit tick timers and watchdog timer in Petra ASIC                                                                                                                                      |                                                                                          |  |

|                        | Two 32-bit tick timers and watchdog timer in VMEchip2 ASIC                                                                                                                                    |                                                                                          |  |

| Software<br>Interrupts | Eight software interrupts (in MVME1X2P4 versions equipped with the VMEchip2 ASIC)                                                                                                             |                                                                                          |  |

| I/O                    | Two EIA-232-D, EIA-530, EIA-422, or EIA-425 configurable serial ports via front panel and transition module                                                                                   |                                                                                          |  |

|                        | Optional SCSI interface with DMA via P2 or LCP2 adapter board                                                                                                                                 |                                                                                          |  |

|                        | Optional Ethernet transceiver interface via DB15 connector on transition module                                                                                                               |                                                                                          |  |

|                        | Four MVIP IndustryPack interface channels with DMA                                                                                                                                            |                                                                                          |  |

Table 1-1. MVME1X2P4 Features Summary (Continued)

| Feature           | MVME162P4                                                                                                                                                                        | MVME172P4 |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| VMEbus            | VMEbus system controller functions                                                                                                                                               |           |

| interface         | VMEbus-to-local-bus interface (A32/A24, D32/D16/D8)                                                                                                                              |           |

|                   | Local-bus-to-VMEbus interface (A16/A24/A32, D8/D16/D32)                                                                                                                          |           |

|                   | Programmable interrupter and interrupt handler                                                                                                                                   |           |

|                   | Global Control/Status register for interprocessor communications                                                                                                                 |           |

|                   | DMA capability for fast local-memory/VMEbus transfers (A16/A24/A32, D16/D32 (D16/D32/D64 BLT)                                                                                    |           |

| Switches          | Two pushbutton switches (ABORT and RESET)                                                                                                                                        |           |

| Status Indicators | Eight LEDs: Board Fail (FAIL), CPU Status (STAT), CPU Activity (RUN), System Controller (SCON), LAN Activity (LAN), Fuse Status (FUSE), SCSI Activity (SCSI), VME Activity (VME) |           |

# **Applicable Industry Standards**

These boards conform to the requirements of the following documents:

- □ VMEbus Specification (IEEE 1014-87)

- □ EIA-232-D Serial Interface Specification, EIA

- □ SCSI Specification, ANSI

- ☐ IndustryPack Specification, GreenSpring

# **Block Diagram**

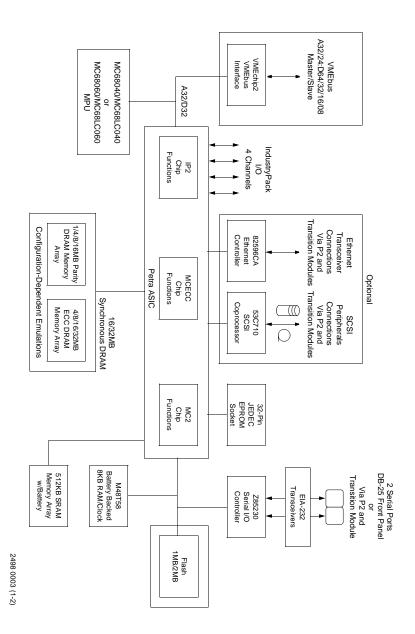

Figure 1-2 is a general block diagram of the MVME1X2P4.

Figure 1-2. MVME1X2P4 Block Diagram

# **Functional Description**

This section highlights a few specific features of the MVME1X2P4 Embedded Controller. For a complete functional description of the major blocks of the MVME1X2P4, refer to the *Installation and Use* manual.

# VMEbus Interface and VMEchip2

The local-bus-to-VMEbus interface and the VMEbus-to-local-bus interface are provided by the VMEchip2 ASIC. The VMEchip2 can also provide the VMEbus system controller functions. Refer to the VMEchip2 description in Chapter 2 for detailed programming information.

In support of possible future configurations in which the MVME1X2P4 might be offered as an embedded controller without the VMEbus interface, certain logic in the VMEchip2 has been duplicated in the Petra chip. Table 1-2 shows the location of the overlapping logic. As long as the VMEchip2 ASIC is present, the redundant logic is inhibited in the Petra chip.

Note that the **ABORT** switch logic in the VMEchip2 is not used. Likewise unused are the GPI inputs to the VMEchip2, which are located at \$FFF40088 bits 7-0. Instead, the **ABORT** switch interrupt is integrated into the Petra ASIC at location \$FFF42043. The GPI inputs are integrated into the Petra ASIC at location \$FFF4202C bits 23-16.

VMEchip2 **Petra Chip** Notes Address Bit # Address Bit # \$FFF42044 \$FFF40060 28-24 28-24 1,5 \$FFF40060 22-19. \$FFF42044 22-19, 2.5 17,16 17,16 \$FFF4004C 13-8 \$FFF42044 13-8 3,5 \$FFF40048 7 \$FFF42048 8 9 \$FFF42048 9 \$FFF40048 4.5 \$FFF40048 10 \$FFF42048 10 4,5 4.5 \$FFF40048 11 \$FFF42048 11 \$FFF40064 31-0 \$FFF4204C 3-0 \$FFF42040 6-0 6 \$FF800000-\$FFBFFFF 31-0 \$FF800000-\$FFBFFFF 31-0

Table 1-2. Functions Duplicated in VMEchip2 and Petra ASICs

#### **Notes**

\$FFE00000-\$FFEFFFF

1. **RESET** switch control.

31-0

- 2. Watchdog timer control.

- 3. Access and watchdog timer parameters.

- 4. MPU TEA (bus error) status

- 5. Bit numbering for the VMEchip2 and Petra ASICs has a one-to-one correspondence.

Programmable

- 6. ABORT switch interrupt control. Implemented also in the VMEchip2, but with a different bit organization (refer to the VMEchip2 description in Chapter 2). In the MVME1X2P4, the ABORT switch is wired to the Petra chip, not the VMEchip2.

- 7. The SRAM and EPROM decoder in the VMEchip2 (version 2) must be disabled by software before any accesses are made to these address spaces.

31-0

7

8. 32-bit prescaler. The prescaler can also be accessed at \$FFF40064 when the optional VMEbus is not enabled.

# **Memory Maps**

There are two points of view for memory maps:

- 1. The mapping of all resources as viewed by local bus masters (local bus memory map)

- 2. The mapping of onboard resources as viewed by VMEbus masters (VMEbus memory map)

The memory maps and I/O maps described in the following tables are correct for all local bus masters. Some address translation capability exists in the VMEchip2. This capability makes it possible to have multiple MVME1X2P4 modules on the same VMEbus with different virtual local bus maps as viewed by different VMEbus masters.

# **Local Bus Memory Map**

The local bus memory map is split into different address spaces by the transfer type (TT) signals. The local resources respond to the normal access and interrupt acknowledge codes.

# **Normal Address Range**

The following tables show the memory maps of devices that respond to the normal address range. The normal address range is defined by the Transfer Type (TT) signals on the local bus. On the MVME1X2P4, Transfer Types 0, 1, and 2 define the normal address range.

Table 1-3 is the entire map from \$00000000 to \$FFFFFFFF. Many areas of the map are user-programmable, and suggested uses are shown in the table. The cache inhibit function is programmable in the MC68xx0x0 MMU. The onboard I/O space must be marked cache inhibit and serialized in its page table. Table 1-4 on page 1-14 further defines the map for the local I/O devices on the MVME1X2P4.

Table 1-3. MVME1X2P4 Local Bus Memory Map

| Address Range         | Devices<br>Accessed | Port<br>Width | Size      | Software<br>Cache<br>Inhibit | Note(s) |

|-----------------------|---------------------|---------------|-----------|------------------------------|---------|

| Programmable          | DRAM on board       | D32           | 4MB-16MB  | N                            | 2       |

| Programmable          | SRAM                | D32           | 128KB-2MB | N                            | 2       |

| Programmable          | VMEbus<br>A32/A24   | D32/D16       |           | ?                            | 4       |