| Cover                                                     | MVME197BUG<br>Diagnostic Firmware<br>(Part 1 of 2) |

|-----------------------------------------------------------|----------------------------------------------------|

| 34 pages                                                  | © TM                                               |

| 1/8" spine<br>36 - 84 pages<br>3/16" & 1/4" spine         | © TM                                               |

| 86 - 100 pages<br>5/16″ spine                             | ® TM                                               |

| 102 - 180 pages                                           | ® TM                                               |

| 3/8″ - 1/2″ spine                                         |                                                    |

| 182 - 308 pages<br>5/8" - 1 1/8" spine<br>2 lines allowed | MVME197BUG Diagnostic Firmware (Part 1 of 2)       |

# MVME197BUG Diagnostic Firmware (Part 1 of 2)

V197DIAA1/UM1

#### Notice

While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

No part of this material may be reproduced or copied in any tangible medium, or stored in a retrieval system, or transmitted in any form, or by any means, radio, electronic, mechanical, photocopying, recording or facsimile, or otherwise, without the prior written permission of Motorola, Inc.

It is possible that this publication may contain reference to, or information about Motorola products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that Motorola intends to announce such Motorola products, programming, or services in your country.

# **Restricted Rights Legend**

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

Motorola, Inc. Computer Group 2900 South Diablo Way Tempe, Arizona 85282-9602

# Preface

This manual provides general information and a description of the diagnostic firmware for the MVME197BUG (197Bug) Debugging Package.

Use of the MVME197 debugger, the debugger command set, use of the one-line assembler/ disassembler, and system calls for the Debugging Package are all described in the *MVME197BUG* (197Bug) Debugging Package User's Manual.

## Note

This document is bound in two parts:

Part 1 (*this volume, V197DIAA1/UM1*) contains Chapters 1 and 2, and the first half of Chapter 3 (pages 3-1 through 138, covering test suites RAM, RAMCDIx, RAMCD, ECDM, DCAM, BSW, XCAx, and MK48T0x).

Part 2 (V197DIAA2/UM1) contains the rest of Chapter 3 (pages 3-139 through 3-302, covering test suites PPC2, CD2401, VME2, LANC, and NCR), Chapter 4, and Appendix A.

The table of contents and index are duplicated in Parts 1 and 2.

This manual is intended for anyone who wants to design OEM systems, supply additional capability to an existing compatible system, or work in a lab environment for experimental purposes. A basic knowledge of computers and digital logic is assumed.

To use this manual, you should be familiar with the publications listed in the *Related Documentation* section found in the following pages.

# Manual Terminology

Throughout this manual, a convention has been maintained whereby data and address parameters are preceded by a character which specifies the numeric format, as follows:

| \$ | dollar    | specifies a hexadecimal number |

|----|-----------|--------------------------------|

| %  | percent   | specifies a binary number      |

| &  | ampersand | specifies a decimal number     |

For example, "12" is the decimal number twelve, and "\$12" is the decimal number eighteen. Unless otherwise specified, all address references are in hexadecimal throughout this manual.

An asterisk (\*) following the signal name for signals which are level significant denotes that the signal is true or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are edge significant denotes that the actions initiated by that signal occur on high to low transition.

In this manual, *assertion* and *negation* are used to specify forcing a signal to a particular state. In particular, *assertion* and *assert* refer to a signal that is active or true; *negation* and *negate* indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

Data and address sizes are defined as follows:

- A *byte* is eight bits, numbered 0 through 7, with bit 0 being the least significant.

- □ A two-byte is 16 bits, numbered 0 through 15, with bit 0 being the least significant. For the MVME197 and other RISC modules, this is called a *halfword*.

- □ A four-byte is 32 bits, numbered 0 through 31, with bit 0 being the least significant. For the MVME197 and other RISC modules, this is called a *word*.

- □ An eight-byte is 64 bits, numbered 0 through 63, with bit 0 being the least significant. For the MVME197 and other RISC modules, this is called a *double-word*.

Throughout this document, it is assumed that the MPU on the MVME197/MVME297 module series is always programmed with *big-endian byte ordering*, as shown below. Any attempt to use *small-endian byte ordering* will immediately render the MVME197Bug debugger unusable.

| BI | Г    |    |    |      |    |    |      |    |    | ]    | BIT |

|----|------|----|----|------|----|----|------|----|----|------|-----|

| 63 |      | 56 | 55 |      | 48 | 47 |      | 40 | 39 |      | 32  |

|    | ADR0 |    |    | ADR1 |    |    | ADR2 |    |    | ADR3 |     |

| 31 |      | 24 | 23 |      | 16 | 15 |      | 08 | 07 |      | 00  |

|    | ADR4 |    |    | ADR5 |    |    | ADR6 |    |    | ADR7 |     |

The terms *control bit* and *status bit* are used extensively in this document. The term *control bit* is used to describe a bit in a register that can be set and cleared under software control. The term *true* is used to indicate that a bit is in the state that enables the function it controls. The term *false* is used to indicate that the bit is in the state that disables the function it controls. In all tables, the terms 0 and 1 are used to describe the actual value that should be written to the bit, or the value that it yields when read. The term *status bit* is used to describe a bit in a register that reflects a specific condition. The status bit can be read by software to determine operational or exception conditions.

The following conventions are used in this document:

#### bold

is used for user input that you type just as it appears. Bold is also used for commands, options and arguments to commands, and names of programs, directories, and files.

#### italic

is used for names of variables to which you assign values. Italic is also used for comments in screen displays and examples.

courier

is used for system output (e.g., screen displays, reports), examples, and system prompts.

#### <RETURN>

represents the Carriage Return or Enter key.

#### CTRL

represents the Control key. Execute control characters by holding down the control key while pressing the letter key, e.g., **CTRL-d**.

# **Related Documentation**

The following publications are applicable to the MVME197 module series and may provide additional helpful information. If not shipped with this product, they may be purchased by contacting your Motorola sales office.

| Document Title                                                                                                         | Motorola<br>Publication Number |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| MVME197LE Single Board Computer User's Manual                                                                          | MVME197LE                      |

| MVME197LE Single Board Computer Support Information                                                                    | SIMVME197LE                    |

| MVME197DP and MVME197SP Single Board Computers<br>User's Manual                                                        | MVME197                        |

| MVME197DP and MVME197SP Single Board Computers<br>Support Information                                                  | SIMVME197                      |

| MVME197LE, MVME197DP, and MVME197SP Single Board<br>Computers Programmer's Reference Guide                             | MVME197PG                      |

| MVME197BUG 197Bug Debugging Package User's Manual                                                                      | MVME197BUG                     |

| MVME712M Transition Module and P2 Adapter Board<br>User's Manual                                                       | MVME712M                       |

| MVME712-12, MVME712-13, MVME712A, MVME712AM,<br>and MVME712B Transition Module and LCP2 Adapter<br>Board User's Manual | MVME712A                       |

| MC88110 Second Generation RISC Microprocessor User's<br>Manual                                                         | MC88110UM                      |

| MC68040 Microprocessor User's Manual                                                                                   | MC68040UM                      |

| MC88410 Secondary Cache Controller User's Manual                                                                       | MC88410UM                      |

# Notes

1. The support information manuals (SIMVME197LE and SIMVME197) contain: the connector interconnect signal information, parts lists, and the schematics for the specific board indicated.

2. Although not shown in the above list, each Motorola Computer Group manual publication number is suffixed with characters which represent the revision level of the document, such as "/D2" (the second revision of a manual); a supplement bears the same number as the manual but has a suffix such as "/A1" (the first supplement to the manual).

To further assist your development effort, Motorola has collected user's manuals for each of the peripheral controllers used on the MVME197 module series and other boards from the suppliers. This bundle includes manuals for the following:

68-1X7DS for use with the MVME197 series of Single Board Computers.

NCR 53C710 SCSI Controller Data Manual and Programmer's Guide Intel i82596 Ethernet Controller User's Manual Cirrus Logic CD2401 Serial Controller User's Manual SGS-Thompson MK48T08 NVRAM/TOD Clock Data Sheet

The following non-Motorola publications may also be of interest and may be obtained from the sources indicated. The VMEbus Specification is contained in ANSI/IEEE Standard 1014-1987.

| ANSI/IEEE Std 1014-1987<br>Versatile Backplane Bus: VMEbus                                      | The Institute of Electrical and Electronics<br>Engineers, Incorporated<br>Publication and Sales Department<br>345 East 47th Street<br>New York, New York 10017-2633<br>Telephone: 1-800-678-4333 |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANSI Small Computer System Interface-2<br>(SCSI-2), Draft Document X3.131-198X,<br>Revision 10c | Global Engineering Documents<br>P.O. Box 19539<br>Irvine, California 92713-9539<br>Telephone (714) 979-8135                                                                                      |

The computer programs stored in the Read Only Memory of this device contain material copyrighted by Motorola Inc., first published 1991, and may be used only under license such as the License for Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

Motorola<sup>®</sup> and the Motorola symbol are registered trademarks of Motorola, Inc.

Delta Series, SYSTEM V/88, VMEmodule, and VMEsystem are trademarks of Motorola, Inc.

Timekeeper and Zeropower are trademarks of Thompson Components.

All other products mentioned in this document are trademarks or registered trademarks of their respective holders

The software described herein and the documentation appearing herein are furnished under a license agreement and may be used and/or disclosed only in accordance with the terms of the agreement.

The software and documentation are copyrighted materials. Making unauthorized copies is prohibited by law. No part of the software or documentation may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means without the prior written permission of Motorola, Inc.

#### DISCLAIMER OF WARRANTY

Unless otherwise provided by written agreement with Motorola, Inc., the software and the documentation are provided on an "as is" basis and without warranty. This disclaimer of warranty is in lieu of all warranties whether express, implied, or statutory, including implied warranties of merchantability or fitness for any particular purpose.

© Copyright Motorola, Inc. 1995

All Rights Reserved Printed in the United States of America August 1995

## CHAPTER 1 197BUG GENERAL INFORMATION

| Overview of M88000 Firmware1-1                  |

|-------------------------------------------------|

| Description of 197Bug1-1                        |

| 197Bug Implementation1-2                        |

| FLASH-Based Debugger1-2                         |

| BOOT ROM1-3                                     |

| Setup System Parameters SETUP1-6                |

| Execute User Program EXEC [ADDR]1-6             |

| Installation and Start-up 1-6                   |

| Autoboot1-6                                     |

| ROMboot1-9                                      |

| Network Boot1-10                                |

| Restarting the System                           |

| Reset                                           |

| Double-Button Reset1-11                         |

| Abort1-12                                       |

| Break 1-13                                      |

| SYSFAIL* Assertion/Negation1-13                 |

| MPU Clock Speed Calculation1-14                 |

| Memory Requirements1-14                         |

| Terminal Input/Output Control1-14               |

| Disk I/O Support1-15                            |

| Blocks Versus Sectors1-16                       |

| Device Probe Function1-16                       |

| Disk I/O via 197Bug Commands 1-17               |

| IOI (Input/Output Inquiry)1-17                  |

| IOP (Physical Input/Output to Disk)1-17         |

| IOT (Input/Output Teach)1-17                    |

| IOC (Input/Output Control)1-18                  |

| BO (Bootstrap Operating System)1-18             |

| BH (Bootstrap and Halt)1-18                     |

| Disk I/O via 197Bug System Calls 1-18           |

| Default 197Bug Controller and Device Parameters |

| Disk I/O Error Codes                            |

| Network I/O Support                             |

| Physical Layer Manager Ethernet Driver 1-20     |

| UDP/IP Protocol Modules<br>RARP/ARP Protocol Modules<br>BOOTP Protocol Module | 1-21 |

|-------------------------------------------------------------------------------|------|

| TFTP Protocol Module                                                          | 1-22 |

| Network Boot Control Module<br>Network I/O Error Codes                        |      |

| Multiprocessor Support<br>Multiprocessor Control Register (MPCR) Method       |      |

| GCSR Method<br>Diagnostic Facilities                                          | 1-24 |

#### CHAPTER 2 DIAGNOSTIC FIRMWARE

| Scope                                                        | 2-1 |

|--------------------------------------------------------------|-----|

| Overview of Diagnostic Firmware                              | 2-1 |

| System Start-up                                              | 2-1 |

| Design Requirements                                          | 2-1 |

| Assembly Language                                            | 2-1 |

| Bug Interface                                                | 2-1 |

| Compatibility                                                | 2-2 |

| Menu Driven                                                  | 2-2 |

| Diagnostic Monitor                                           | 2-2 |

| Monitor Start-up                                             | 2-2 |

| Command Entry and Directories                                | 2-3 |

| Utilities                                                    | 2-4 |

| All Errors Mode - Command AE                                 | 2-5 |

| Append Error Messages Mode - Command AEM                     |     |

| Clear Error Messages - Command CEM                           |     |

| Test Group Configuration (cf) Parameters Editor - Command CF | 2-5 |

| Display Error Counters - Command DE                          |     |

| Display Error Messages - Command DEM                         | 2-6 |

| Display Pass Count - Command DP                              | 2-6 |

| Help - Command HE                                            | 2-6 |

| Help Extended - Command HEX                                  | 2-6 |

| Loop Always Mode - Prefix LA                                 | 2-8 |

| Loop-Continue Mode - Prefix LC                               |     |

| Loop-On-Error Mode - Prefix LE                               | 2-8 |

| Line Feed Suppression Mode - Prefix LF                       | 2-8 |

| Loop Non-Verbose Mode - Prefix LN                            | 2-9 |

| Display/Revise Self Test Mask - Command MASK                 | 2-9 |

| Non-Verbose Mode - Prefix NV                                 |     |

| Switch Directories - Command SD          |  |

|------------------------------------------|--|

| Stop-On-Error Mode - Prefix SE           |  |

| Self Test - Command ST                   |  |

| Clear (Zero) Error Counters - Command ZE |  |

| Zero Pass Count - Command ZP             |  |

## CHAPTER 3 TEST DESCRIPTIONS

| Local RAM (RAM) Tests                                         | 3-3  |

|---------------------------------------------------------------|------|

| RAM Configuration Parameters                                  | 3-5  |

| Memory Addressing - ADR                                       | 3-8  |

| Alternating Ones/Zeros - ALTS 3                               | 3-10 |

| Bit Toggle - BTOG                                             | 3-11 |

| Code Execution/Copy - CODE 3                                  | 3-13 |

| March Address - MARCH 3                                       | 3-14 |

| Data Patterns - PATS 3                                        |      |

| Byte/Half/Word Permutations - PERM 3                          |      |

| Quick Write/Read - QUIK 3                                     |      |

| Memory Refresh Testing - REF 3                                | 3-21 |

| Random Data - RNDM 3                                          | 3-23 |

| RAM Common Test Error Messages 3                              |      |

| Local RAM (RAMCDIx) Tests with Caching (Data and Instruction) | 3-28 |

| RAMCDIx Configuration Parameters 3                            |      |

| Local RAM (RAMCD) Tests with Caching (Data only)              | 3-31 |

| RAMCD Configuration Parameters 3                              | 3-32 |

| Error Correcting Data Multiplexer (ECDM) ASIC Tests           | 3-33 |

| ECDM Configuration Parameters                                 | 3-35 |

| Checkbit Generation - CHKGEN 3                                | 3-37 |

| Checkbit DRAM Test - CHKRAM 3                                 | 3-39 |

| DBE Control Options - DBEC 3                                  | 3-41 |

| DBE Permutations - DBEP 3                                     | 3-45 |

| I2CBus Interface Check - I2C 3                                |      |

| INIT Function Check - INITCK 3                                |      |

| DRAM Sub-System Mapping - MAP 3                               | 3-53 |

| Register Checks - REGS                                        | 3-55 |

| SBE Control Options - SBEC 3                                  |      |

| Permutations - SBEP 3                                         | 3-61 |

| ECDM Common Test Error Messages 3                             |      |

| DRAM Controller and Address Multiplexer (DCAM) Utilities      |      |

| DCAM Configuration Parameters 3                               |      |

| DCAM Register Display - RD 3                                  | 3-69 |

| DCAM Register Modify - RM                     |          |

|-----------------------------------------------|----------|

| BusSwitch ASIC (BSW) Tests                    |          |

| BSW Configuration Parameters                  | )<br>-   |

| Cross Processor Interrupts - CPINT            |          |

| Dynamic CPINT Extensions: Internal - CPINTI   |          |

| Dynamic CPINT Extensions: External - CPINTX   |          |

| Interrupt Steering Test - ISTR                |          |

| Memory Error Interrupt - MERR                 | <i>;</i> |

| Prescaler Clock Adjust - PADJ                 |          |

| Prescaler/Clock Accuracy - PCLK               | ;<br>-   |

| Register Checks - REGS                        | ,        |

| Spurious Interrupt - SPINT                    | ;        |

| Tick Timer 1 Counter Verification - TMR1A     |          |

| Tick Timer 1 Free-Run - TMR1B                 |          |

| Tick Timer 1 Clear On Compare - TMR1C         |          |

| Tick Timer 1 Overflow Counter - TMR1D         | t .      |

| Tick Timer 1 Interrupts - TMR1E               | ,        |

| Tick Timer 2 Counter Verification - TMR2A     |          |

| Tick Timer 2 Free-Run - TMR2B                 |          |

| Tick Timer 2 Clear On Compare - TMR2C         | ,        |

| Tick Timer 2 Overflow Counter - TMR2D 3-114   | ŧ        |

| Tick Timer 2 Interrupts - TMR2E 3-116         | )        |

| Vector Base Register - VBR                    |          |

| External Interrupt - XINT                     |          |

| External Cache MC88410/MC62110 (XCAx) Tests   |          |

| XCAx Configuration Parameters 3-125           |          |

| External Cache Ptag Test - PTAG 3-126         | )        |

| External Cache Mtag Test - MTAG 3-128         |          |

| External Cache Data Test - DATA 3-130         |          |

| External Cache Sliding Bit Test - SLIDE 3-132 |          |

| MK48T0x (RTC) Tests                           |          |

| RTC Configuration Parameters 3-135            |          |

| BBRAM Addressing - ADR 3-136                  |          |

| Clock Function - CLK 3-138                    |          |

| Battery Backed-Up SRAM - RAM 3-141            |          |

| Peripheral Channel Controller (PCC2) Tests    | 3        |

| PCC2 Configuration Parameters 3-145           | 5        |

| Prescaler Clock Adjust - ADJ 3-146            | ;<br>)   |

| FAST Bit - FAST                               |          |

| GPIO Interrupts - GPIO 3-150                  |          |

| LANC Interrupts - LANC                        |          |

| 1                                             |          |

|    | MIEN Bit - MIEN                                       | 3-156 |

|----|-------------------------------------------------------|-------|

|    | Prescaler Clock - PCLK                                | 3-158 |

|    | Printer ACK Interrupts - PRNTA                        |       |

|    | Printer FAULT Interrupts - PRNTB                      |       |

|    | Printer SEL Interrupts - PRNTC                        |       |

|    | Printer PE Interrupts - PRNTD                         |       |

|    | Printer BUSY Interrupts - PRNTE                       | 3-172 |

|    | Device Access - REGA                                  | 3-175 |

|    | Register Access - REGB                                |       |

|    | Timer 1 Counter - TMR1A                               | 3-179 |

|    | Timer 1 Free-Run - TMR1B                              | 3-181 |

|    | Timer 1 Clear On Compare - TMR1C                      | 3-183 |

|    | Timer 1 Overflow Counter - TMR1D                      | 3-184 |

|    | Timer 1 Interrupts - TMR1E                            | 3-186 |

|    | Timer 2 Counter - TMR2A                               | 3-189 |

|    | Timer 2 Free-Run - TMR2B                              | 3-191 |

|    | Timer 2 Clear On Compare - TMR2C                      | 3-193 |

|    | Timer 2 Overflow Counter - TMR2D                      | 3-194 |

|    | Timer 2 Interrupts - TMR2E                            | 3-196 |

|    | Vector Base Register - VBR                            | 3-199 |

| CD | 2401 Serial Port (ST2401) Tests                       |       |

|    | ST2401 Configuration Parameters                       | 3-202 |

|    | Baud Rates, Async, Internal Loopback - BAUD           | 3-203 |

|    | DMA I/O, Async, Internal Loopback - DMA               | 3-205 |

|    | Interrupt I/O, Async, Internal Loopback - INTR        |       |

|    | Polled I/O, Async, Internal Loopback - POLL           |       |

|    | ST2401 Common Test Error Messages                     | 3-211 |

| VM | E Interface ASIC (VME2) Tests                         | 3-213 |

|    | VME2 Configuration Parameters                         | 3-215 |

|    | Register Access - REGA                                | 3-217 |

|    | Register Walking Bit - REGB                           |       |

|    | Software Interrupts (Polled Mode) - SWIA              | 3-221 |

|    | Software Interrupts (Processor Interrupt Mode) - SWIB | 3-223 |

|    | Software Interrupts Priority - SWIC                   |       |

|    | Timer Accuracy Test - TACU                            | 3-229 |

|    | Timer Increment - TMRA, TMRB                          | 3-231 |

|    | Prescaler Clock Adjust - TMRC                         |       |

|    | Tick Timer No Clear On Compare - TMRD, TMRE           | 3-235 |

|    | Tick Timer Clear On Compare - TMRF, TMRG              | 3-237 |

|    | Overflow Counter - TMRH, TMRI                         |       |

|    | Watchdog Timer Counter - TMRJ                         | 3-241 |

|    |                                                       |       |

| Watchdog Timer Board Fail - TMRK          |       |

|-------------------------------------------|-------|

| LAN Coprocessor for Ethernet (LANC) Tests |       |

| LANC Configuration Parameters             | 3-246 |

| Bus Error - BERR                          |       |

| Chip Self Test - CST                      |       |

| Diagnose Internal Hardware - DIAG         |       |

| Dump Configuration/Registers - DUMP       | 3-256 |

| External Loopback Cable - ELBC            |       |

| External Loopback Transceiver - ELBT      |       |

| +12VDC Fuse - FUSE                        |       |

| Internal Loopback - ILB                   |       |

| Interrupt Request - IRQ                   |       |

| Monitor (Incoming Frames) Mode - MON      |       |

| Time Domain Reflectometry - TDR           |       |

| Additional Error Messages                 |       |

| SCSI I/O Processor (NCR) Tests            |       |

| NCR Configuration Parameters              |       |

| Device Access - ACC1                      |       |

| Register Access - ACC2                    |       |

| DMA FIFO - DFIFO                          |       |

| DMA SCRIPTs Utility - DMA                 |       |

| Interrupts - IRQ                          |       |

| Loopback - LPBK                           |       |

| SCRIPTs Processor - SCRIPTS               |       |

| SCSI FIFO - SFIFO                         |       |

|                                           |       |

#### CHAPTER 4 197BUG GENERAL INFORMATION

| Introduction                                  | 4-1 |

|-----------------------------------------------|-----|

| Configure Board Information Block - CNFG      | 4-1 |

| Set Environment to Bug/Operating System - ENV |     |

| Configuring Parameters with ENV               |     |

| Configuring the VMEbus Interface              |     |

#### APPENDIX A MVME197 FAMILY DRAM MEMORY LINE MAPPING

# **Figures**

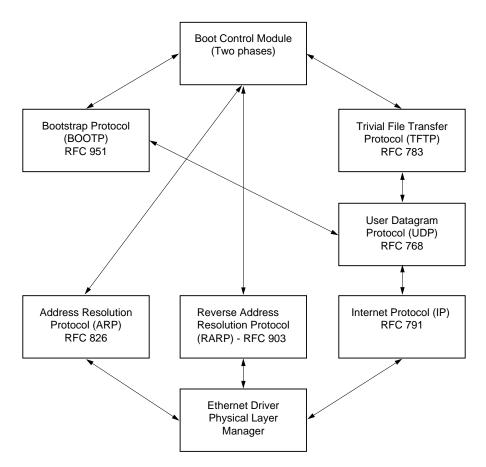

| Figure 1-1. | Network Boot Modules                    | 1-21 |

|-------------|-----------------------------------------|------|

| Figure 2-1. | Help Screen                             | 2-7  |

| 0           | MVME197 Family DRAM Memory Line Mapping |      |

# Tables

| Table 1-1. | BootBug Debugger Commands | 1-3 |

|------------|---------------------------|-----|

| Table 1-2. | SETUP and EXEC Commands   |     |

| Table 2-1. | Diagnostic Utilities      | 2-4 |

| Table 3-1. | Diagnostic Test Groups    |     |

| Table 3-2. | RAM Test Group            |     |

| Table 3-3. | RAMCDIx Test Groups       |     |

| Table 3-4. | RAMCD Test Group          |     |

|            | ECDM Test Group           |     |

| Table 3-6. | DCAM Test Group           |     |

| Table 3-7. | BSW Test Group            |     |

| Table 3-8. | XCAx Test Group           |     |

| Table 3-9. | RTC Test Group            |     |

| Table 3-10 | . PCC2 Test Group         |     |

| Table 3-11 | . ST2401 Test Group       |     |

| Table 3-12 | . Baud Rates              |     |

| Table 3-13 | . VME2 Test Group         |     |

| Table 3-14 | . LANC Test Group         |     |

| Table 3-15 | . NCR Test Group          |     |

|            |                           |     |

# 197BUG GENERAL INFORMATION

# **Overview of M88000 Firmware**

The firmware for the M88000-based (88K) series of board and system level products has a common genealogy, deriving from the BUG firmware currently used on all Motorola M68000-based (68K) CPU modules.

The M88000 firmware family provides:

- □ A high degree of functionality

- □ User friendliness

- Portability

- **D** Ease of maintenance

This member of the M88000 Firmware family is implemented on all of the MVME197 series of Single Board Computers, and is known as the MVME197BUG, or just 197Bug.

# **Description of 197Bug**

The 197Bug package, MVME197BUG, is a powerful evaluation and debugging tool for systems built around the MVME197 series of RISC-based (Reduced Instruction Set Computing) microcomputers.

197Bug consists of three parts:

- □ A command-driven user-interactive software debugger, described in the *MVME197BUG 197Bug Debugging Package User's Manual*. It is hereafter referred to as "the debugger", "197Bug", or just "Bug"

- □ A command-driven diagnostic package for the MVME197 hardware, described in this manual. It is hereafter referred to as "the diagnostics"

- □ A user interface which accepts commands from the system console terminal

When using 197Bug, the user operates out of either:

- □ The debugger directory or

- □ The diagnostic directory

If you are in the debugger directory, then the debugger prompt "**197-Bug>**" is displayed and you have all of the debugger commands at your disposal. If you

are in the diagnostic directory, then the diagnostic prompt "**197-Diag>**" is displayed and you have all of the diagnostic commands at your disposal as well as all of the debugger commands.

You may switch between directories by using the Switch Directories (**SD**) command (refer to the *MVME197BUG 197Bug Debugging Package User's Manual*), or may examine the commands in the particular directory that you are currently in by using the Help (**HE**) command (refer to the *MVME197BUG 197Bug Debugging Package User's Manual*).

Because 197Bug is command-driven, it performs its various operations in response to user commands entered at the keyboard. The flow of control in 197Bug is explained in the following section. When a command is entered, 197Bug executes the command and the prompt reappears. However, if a command is entered which causes execution of user target code (e.g., "**GO**"), then control may or may not return to 197Bug, depending on the outcome of the user program.

# **197Bug Implementation**

## FLASH-Based Debugger

197Bug is contained in the FLASH memory devices located on the MVME197 board. The FLASH devices are electrically re-writable and may be reprogrammed without removing the physical devices from the MVME197 board. This allows you to incorporate updated versions of the 197Bug as they become available by simply loading the newer version into the FLASH memory and overwriting the older version.

The **PFLASH** command (refer to the *MVME197BUG 197Bug Debugging Package User's Manual*) describes how to reprogram the FLASH memory contents. The executable code is checksummed at every power-on or reset firmware entry. You are cautioned against reprogramming of the FLASH memory contents unless rechecksum precautions are taken. Refer to the **CS** command description in the *MVME197BUG 197Bug Debugging Package User's Manual* for checksum information.

Reprogramming any portion of FLASH memory will erase everything currently contained in FLASH, including the debugger. A valid version of 197Bug must be transferred from RAM into the FLASH during FLASH reprogramming in order for the debugger to operate. The 197Bug Debugger Command Set chapter of the MVME197BUG 197Bug Debugging Package User's Manual describes the command set of the FLASH-based debugger.

# **BOOT ROM**

A subset of 197Bug is also programmed into the BOOT ROM, which is an EPROM or One-Time Programmable ROM on the MVME197 module. This scaled-down 197Bug is referred to as the "BootBug", or "197BBug".

When the MVME197 module is reset, control is first given to the code which resides in the BOOT ROM. During normal operation, the BOOT ROM passes control quickly to the debugger residing in the FLASH memory.

It is possible to prevent control from being passed to the FLASH-based debugger and to continue execution of the BOOT ROM code (or BootBug). This may be done by performing a "double-button RESET". Refer to the *Double-Button Reset* section later in this chapter.

The BootBug, due to its limited size, does not support the entire command set of the FLASH-based debugger, but contains enough functionality to enable downloading of object code (by means of the VMEbus, serial port, SCSI bus or the network) and reprogramming of the FLASH memory. Some versions of the BootBug may not contain both network commands (**NIOT**, **NIOP**) and disk/tape commands (**IOT**, **IOP**) because of ROM-space constraints.

The following table lists the debugger commands of the BootBug.

| Command<br>Mnemonic | Command<br>Title           | Command Line<br>Syntax                                                             |

|---------------------|----------------------------|------------------------------------------------------------------------------------|

| ВС                  | Block of Memory<br>Compare | BC RANGE DEL ADDR [; B   H   W]                                                    |

| BF                  | Block of Memory<br>Fill    | <b>BF</b> RANGE DEL data [DEL increment] [; <b>B</b>   <b>H</b>   <b>W</b> ]       |

| ВМ                  | Block of Memory<br>Move    | BM RANGE DEL ADDR [; B   H   W]                                                    |

| BS                  | Block of Memory<br>Search  | BS RANGE DEL TEXT [;B   H   W] or<br>BS RANGE DEL data DEL [mask] [;B   H   W,N,V] |

Table 1-1. BootBug Debugger Commands

| Command<br>Mnemonic | Command<br>Title                                  | Command Line<br>Syntax                                                                       |

|---------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------|

| BV                  | Block of Memory<br>Verify                         | <b>BV</b> <i>RANGE DEL data</i> [ <i>DEL increment</i> ] [; <b>B</b>   <b>H</b>   <b>W</b> ] |

| CS                  | Checksum                                          | CS RANGE [;B   H   W]                                                                        |

| DC                  | Data Conversion                                   | DC EXP   ADDR [;[B] [O] [A]]                                                                 |

| HE                  | Help on<br>Command(s)                             | HE [COMMAND]                                                                                 |

| IOP                 | I/O Physical<br>(Direct Disk<br>Access)           | IOP                                                                                          |

| IOT                 | I/O "TEACH" for<br>Configuring Disk<br>Controller | IOT [;[A F H T]                                                                              |

| LO                  | Load S-Records<br>from Host                       | LO [PORT] [DEL ADDR] [;[X][C][T] [=text]                                                     |

| MD                  | Memory Display                                    | $\mathbf{MD}[\mathbf{S}] ADDR [:COUNT   DEL ADDR] [; [\mathbf{B}   \mathbf{H}   \mathbf{W}]$ |

| MM                  | Memory Modify                                     | MM ADDR [;[B   H   W] [A] [N] ]                                                              |

| MS                  | Memory Set                                        | <b>MS</b> ADDR DEL {Hexadecimal Number}/{'String'}                                           |

| NIOP                | Network I/O<br>Physical                           | NIOP                                                                                         |

| NIOT                | Network I/O<br>Teach                              | NIOT [;[H]   [A]]                                                                            |

| NOPF                | Port Detach                                       | NOPF [PORT]                                                                                  |

| PF                  | Port Format                                       | PF [PORT]                                                                                    |

Table 1-1. BootBug Debugger Commands (Continued)

| Command<br>Mnemonic | Command<br>Title                   | Command Line<br>Syntax                                                                                                      |

|---------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| PFLASH              | Program FLASH<br>Memory            | PFLASH SSADDR SEADDR DSADDR<br>[IEADDR] [;[A   R] [X]]<br>PFLASH SSADDR:COUNT DSADDR<br>[IEADDR] [;[B   H   W] [A   R] [X]] |

| SET                 | Set Time and Date                  | <b>SET</b> [ <i>mmddyyhhmm</i> ]   [<+/-CAL:>; <b>C</b> ]                                                                   |

| TIME                | Display Time and<br>Date           | TIME [;C L O]                                                                                                               |

| ТМ                  | Transparent Mode                   | TM [PORT] [DEL ESCAPE]                                                                                                      |

| VE                  | Verify S-records<br>Against Memory | <b>VE</b> [ <i>n</i> ] [ <i>ADDR</i> ] [; <b>X</b>   <b>C</b> ] [= <i>text</i> ]                                            |

Table 1-1. BootBug Debugger Commands (Continued)

Detailed descriptions of these commands may be found in the *MVME197BUG* 197Bug Debugging Package User's Manual.

The BootBug contains two additional commands that are not found in the command set of the FLASH-based debugger. These are the **SETUP** command and the **EXEC** command. The following table lists these two commands.

| Command<br>Mnemonic | Command<br>Title           | Command Line<br>Syntax |

|---------------------|----------------------------|------------------------|

| EXEC                | Execute User<br>Program    | EXEC [ADDR]            |

| SETUP               | Setup System<br>Parameters | SETUP                  |

Table 1-2. SETUP and EXEC Commands

Before using some of the features of the BootBug, some parameters may need to be defined. Some examples are the SCSI ID, the Ethernet address, the clock speed of the board, and the mapping of the VMEbus. The **SETUP** command has been provided for this purpose. Run this command and answer the

prompts to be sure the board is configured properly before using any SCSI, VME, or Ethernet I/O.

#### Setup System Parameters SETUP

**SETUP** allows configuring certain parameters that are necessary for some I/O operations (SCSI, VME, and Ethernet). When this command is executed, the operator is prompted for input after displaying the default value, if any is available.

The **SETUP** command VME parameters do not stay through a reset. These parameters are not saved to NVRAM. The remaining parameters (MPU Clock Speed, Ethernet Address, Local SCSI Identifier) are saved to NVRAM, but are not checksummed.

```

197-BBug>setup

MPU Clock Speed

= "4000"?

Ethernet Address

= 08003E21F959?

Local SCSI Identifier = "07"?

VME Slave Enable #1 [Y/N]

= N?

VME Slave Starting Address

= 0000000?

VME Slave Ending Address

= 0000FFFF?

VME Slave Address Translation Address = 00000000?

VME Slave Address Translation Select = 00000000?

VME Slave Control

= 0000?

= Y?

= 40000000?

= 4FFFFFF?

VME Master Enable [Y/N]

VME Master Starting Address

VME Master Ending Address

VME Master Address Translation Address = 00000000?

VME Master Address Translation Select = 00000000?

VME Master Control

= 0D?

197-BBug>

```

#### Execute User Program EXEC [ADDR]

The **EXEC** command is used to start code execution at a particular address. Execution is transferred to the specified address ("ADDR").

# Installation and Start-up

Even though the MVME197Bug flash memory devices are installed on the MVME197 module, for 197Bug to operate properly with the MVME197, follow this set-up procedure.

# Inserting or removing modules while power is applied could damage module components.

- 1. Turn all equipment power OFF. Refer to the board specific MVME197 User's Manual for selecting the configuration switch settings required for the user's particular application.

- 2. Refer to the set-up procedure for the user's particular chassis or system for details concerning the installation of the MVME197.

- 3. Connect the terminal which is to be used as the 197Bug system console to the default debug EIA-232-D port at serial port 1 on backplane connector P2 through an MVME712X transition module. Refer to the *MVME197LE*, *MVME197DP*, and *MVME197SP Single Board Computers Programmer's Reference Guide* for some possible connection diagrams.

Set up the terminal as follows:

- eight bits per character

- one stop bit per character

- parity disabled (no parity)

- baud rate 9600 baud (default baud rate of the MVME197 ports at power-up)

After power-up, the baud rate of the debug port can be reconfigured by using the Port Format (**PF**) command of the 197Bug debugger.

#### Note

In order for high-baud rate serial communication between 197Bug and the terminal to work, the terminal must do some form of handshaking. If the terminal being used does not do hardware handshaking via the CTS line, then it must do XON/XOFF handshaking. If you get garbled messages and missing characters, then you should check the terminal to make sure XON/XOFF handshaking is enabled.

4. If it is desired to connect devices (such as a host computer system and/or a serial printer) to the other EIA-232-D port connectors (marked SERIAL PORTS 2, 3, and 4 on the MVME712X transition module), connect the appropriate cables and configure the port(s) as detailed in step 3 above.

After power-up, this(these) port(s) can be reconfigured by programming the MVME197 CD2401 Serial Controller Chip (SCC), or by using the 197Bug **PF** command.

Note that the MVME197 also contains a parallel port. To use a parallel device, such as a printer, with the MVME197, connect it to the "printer" port at P2 through an MVME712X transition module. Refer to the *MVME197LE*, *MVME197DP*, and *MVME197SP Single Board Computers Programmer's Reference Guide* for some possible connection diagrams.

5. Power up the system. 197Bug executes some self-checks and displays the debugger prompt "197-Bug>" (if 197Bug is in Board Mode). However, if the ENV command has put 197Bug in System Mode, the system performs a self-test and enters the Menu mode. Refer to the ENV and MENU commands in the MVME197BUG 197Bug Debugging Package User's Manual.

All self-tests are executed unless masked by the Diagnostic Mask command. If a test fails, any error messages are preserved in the Diagnostic error message buffer and execution continues to the next test after issuing a CRLF to preserve the test failure banner. At the conclusion of the self-test, a list of any failed tests will remain on the display and the Display Error Messages (DEM) command may be used from the 197-Diag> prompt to see any detailed error information resulting from the execution of the self-tests.

# Autoboot

Autoboot is a 197Bug software routine that provides an independent mechanism for booting an operating system. This autoboot routine automatically scans for controllers and devices in a specified sequence until a valid bootable device containing a boot media is found or the list is exhausted. If a valid bootable device is found, a boot from that device is started. The controller scanning sequence goes from the lowest controller Logical Unit Number (LUN) detected to the highest LUN detected.

At power-up, if Autoboot is enabled, and providing the drive and controller numbers encountered are valid, the following message is displayed upon the system console:

```

"Autoboot in progress... To abort hit <BREAK>"

```

Following this message there is approximately a thirty-second delay while the debug firmware waits for the various controllers and drives to come up to speed. Then the actual I/O is begun: the program pointed to within the volume ID of the media specified is loaded into RAM and control passed to it. If, however, during this time you want to gain control without Autoboot, the <BREAK> key or the ABORT or RESET switches can be pressed.

Autoboot is controlled by parameters contained in the **ENV** command. These parameters allow the selection of specific boot devices and files, and allow programming of the Boot delay. Refer to the **ENV** command in the *MVME197BUG 197Bug Debugging Package User's Manual* for more details.

Although streaming tape can be used to autoboot, the same power supply must be connected to the streaming tape drive, controller, and the MVME197. At power-up, the tape controller will position the streaming tape to load point where the volume ID can correctly be read and used.

If, however, the MVME197 loses power but the controller does not, and the tape happens not to be at load point, the sequences of commands required (attach and rewind) cannot be given to the controller and autoboot will not be successful.

# ROMboot

This function is configured/enabled by the Environment (**ENV**) command and executed at power-up (optionally also at reset) or by the **RB** command assuming there is valid code in the flash memories (or optionally elsewhere on the module or VMEbus) to support it. If user-supplied ROMboot code is installed, the routine is given control (if the routine meets the format requirements). The **NORB** command disables the function.

For a user's ROMboot module to gain control through the ROMboot linkage, four requirements must be met:

- 1. Power must have just been applied (but the **ENV** command can change this to also respond to any reset).

- 2. The user's routine must be located within the MVME197 ROM memory map (but the **ENV** command can change this to any other portion of the onboard memory, or even offboard VMEbus memory).

- 3. The ASCII string "BOOT" must be located within the specified memory range.

- 4. The user's routine must pass a checksum test, which ensures that this routine was really intended to receive control at power-up.

For complete details on how to use ROMboot, refer to the *MVME197BUG* 197Bug Debugging Package User's Manual.

1

# **Network Boot**

Network Auto Boot is a 197Bug software routine that provides a mechanism for booting an operating system using a network (local Ethernet interface) as the boot device. The Network Auto Boot routine automatically scans for controllers and devices in a specified sequence until a valid bootable device containing a boot media is found or the list is exhausted. If a valid bootable device is found, a boot from that device is started. The controller scanning sequence goes from the lowest controller Logical Unit Number (LUN) detected to the highest LUN detected.

At power-up, Network Boot is enabled, and providing the drive and controller numbers encountered are valid, the following message is displayed upon the system console:

"Network Boot in progress... To abort hit <BREAK>"

Following this message there is approximately a thirty-second delay while the debug firmware waits for the various controllers and drives to come up to speed. Then the actual I/O is begun: the program pointed to within the volume ID of the media specified is loaded into RAM and control passed to it. If, however, during this time you want to gain control without Network Boot, you can press the <BREAK> key or the ABORT or RESET switches.

Network Auto Boot is controlled by parameters contained in the **NIOT** and **ENV** commands. These parameters allow the selection of specific boot devices, systems, and files, and allow programming of the Boot delay. Refer to the **NIOT** and **ENV** commands in the *MVME197BUG 197Bug Debugging Package User's Manual* for more details.

# **Restarting the System**

You can initialize the system to a known state in three different ways: reset, abort, and break. Each has characteristics which make it more appropriate than the others in certain situations.

# Reset

Pressing and releasing the MVME197 front panel reset switch initiates a system reset (if the board is the System Controller). A system reset also occurs if power is removed from the MVME197 module and then reapplied. Reset is used to restore the system to a known state. The debugger environment (refer to the ENV command description in the *MVME197BUG 197Bug Debugging Package User's Manual*) is restored to the user-selected defaults, which had been stored to NVRAM and were preserved through the reset.

COLD and WARM reset modes are available and are selected using the **RESET** command. By default, 197Bug is in COLD mode (refer to the **RESET** command description in the *MVME197BUG 197Bug Debugging Package User's Manual*).

During COLD reset, a total system initialization takes place, as if the MVME197 had just been powered up:

- All static variables (including disk device and controller parameters) are restored to their default states

- □ The breakpoint table and offset registers are cleared

- □ The target registers are invalidated. Input and output character queues are cleared

- Onboard devices are reset

- □ The first two serial ports are reconfigured to their default state

During WARM reset, the 197Bug variables and tables are preserved, as well as the target state registers and breakpoints.

Reset must be used if the processor ever halts, or if the 197Bug environment is ever lost (vector table is destroyed, stack corrupted, etc.).

#### **Double-Button Reset**

Immediately after reset, control is given to the BootBug. During normal operation, the BootBug quickly passes control to the full debugger which resides in FLASH memory. This code then initializes the board and the debugger environment from the user-specified defaults. In some cases, however, it is desirable to not follow this normal flow after reset. This may be the case if the FLASH memory has been corrupted or if the user-specified parameters in the NVRAM prevent proper board initialization.

It is possible to prevent control from being passed to the FLASH-based debugger and to continue execution of the BOOT ROM code (or BootBug). This may be done by performing a "double-button RESET". Press both the **ABORT** and **RESET** push-buttons simultaneous and then release the RESET push-button but continue to press the ABORT push-button for approximately 2 seconds before releasing.

The BootBug banner will appear and a prompt message will query the user whether to transfer control to the FLASH-based debugger (with the factoryprogrammed defaults for board initialization and debugger environment):

```

Copyright Motorola Inc. 1993, All Rights Reserved

MVME197 Boot Debugger Release Version 0.5 - 08/09/93

Continue in Debugger with Double Button Reset? (N/Y)?

```

If the answer is "Y", control will be passed to the FLASH version of the debugger and the user-selected defaults, stored in NVRAM, will not be used. This can be helpful if invalid parameters have inadvertently been written to NVRAM, thus interfering with normal start-up.

If the answer is "N", then control is not passed to the FLASH-based debugger. Instead the BootBug initializes the board and issues its own prompt:

```

197-BBug>

```

It is helpful to remain in the BootBug if the FLASH has been mis-programmed and normal RESET causes the board to hang.

The BootBug, due to its limited size, does not support the entire command set of the FLASH-based debugger, but contains enough functionality to enable downloading of object code by means of the VMEbus, serial port, SCSI bus, or the network and reprogramming of the FLASH memory. Some versions of the BootBug may not contain both network commands (**NIOT** and **NIOP**) and disk/tape commands (**IOT** and **IOP**) because of ROM-space constraints.

#### Abort

Abort is invoked by pressing and releasing the ABORT switch on the MVME197 front panel. Whenever abort is invoked when executing a user program (running target code), a "snapshot" of the processor state is captured and stored in the target registers.

When working in the debugger, abort captures and stores only the following:

- □ Instruction Pointer (IP)

- Status register

- □ Format/vector information

For this reason, abort is most appropriate when terminating a user program that is being debugged. Abort should be used to regain control if the program gets caught in a loop, etc. The target IP, register contents, etc., help to pinpoint the malfunction.

Pressing and releasing the ABORT switch causes the following:

- □ Interrupt to the microprocessor

- □ The target registers, reflecting the machine state at the time the ABORT switch was pressed, are displayed on the screen

- □ Any breakpoints installed in the user code are removed

- □ The breakpoint table remains intact

- □ Control is returned to the debugger

#### Break

A "Break" is generated by pressing and releasing the BREAK key on the terminal keyboard. Break does not generate an interrupt. The only time break is recognized is when characters are sent or received by the console port.

Break performs the following:

- □ Removes any breakpoints in the user code

- □ Keeps the breakpoint table intact

- □ Takes a snapshot of the machine state if the function was entered using SYSCALL

- □ Allows access to the snapshot for diagnostic purposes

Many times it is desired to terminate a debugger command prior to its completion, for example, the display of a large block of memory. Break normally allows the user to terminate the command.

#### SYSFAIL\* Assertion/Negation

Upon a reset/power up condition the debugger asserts the VMEbus SYSFAIL\* line (refer to the VMEbus specification). SYSFAIL\* stays asserted if any of the following has occurred:

- □ Confidence test failure

- NVRAM checksum error

- □ Local memory configuration status

- □ Self test (if system mode) has completed with error

- □ MPU clock speed calculation failure

After debugger initialization is done and any of the above situations has not occurred, the SYSFAIL\* line is negated. This indicates to the user or VMEbus masters the state of the debugger. In a multi-computer configuration, other VMEbus masters could view the pertinent control and status registers to

determine which CPU is asserting SYSFAIL\*. SYSFAIL\* assertion/negation is also affected by the **ENV** command. Refer to the *MVME197BUG 197Bug Debugging Package User's Manual*.

## **MPU Clock Speed Calculation**

The clock speed of the microprocessor is calculated and checked against a user definable parameter housed in NVRAM (refer to the **ENV** command). If the check fails, a warning message is displayed. The calculated clock speed is also checked against known clock speeds and tolerances.

# **Memory Requirements**

The program portion of 197Bug is approximately 1 megabyte of code, consisting of download, debugger, and diagnostic packages and contained entirely in the flash memory. The flash memory on the MVME197 is mapped starting at location \$FF800000.

197Bug requires a minimum of 64K bytes of contiguous read/write memory to operate. The **ENV** command controls where this block of memory is located. Regardless of where the onboard RAM is located, the first 64K bytes is used for 197Bug stack and static variable space and the rest is reserved as user space. Whenever the MVME197 is reset, the target IP is initialized to the address corresponding to the beginning of the user space, and the target stack pointers are initialized to addresses within the user space, with the target Pseudo Stack Pointer (R31) set to the top of the user space.

#### **Terminal Input/Output Control**

When entering a command at the prompt, the following control codes may be entered for limited command line editing.

# Note

# The presence of the upward caret, "^", before a character indicates that the Control (CTRL) key must be held down while striking the character key.

\*X (cancel line) The cursor is backspaced to the beginning of the line. If the terminal port is configured with the hardcopy or TTY option (refer to the **PF** command), then a carriage return and line feed is issued along with another prompt.

1

| ^H          | (backspace)        | The cursor is moved back one position. The character at the new cursor position is erased. If the hardcopy option is selected, a "/" character is typed along with the deleted character.                                                                                                                                           |

|-------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <del></del> | (delete or rubout) | Performs the same function as <b>^H</b> .                                                                                                                                                                                                                                                                                           |

| ^D          | (redisplay)        | The entire command line as entered so far is redisplayed on the following line.                                                                                                                                                                                                                                                     |

| ^A          | (repeat)           | Repeats the previous line. This happens only<br>at the command line. The last line entered is<br>redisplayed but not executed. The cursor is<br>positioned at the end of the line. You may<br>enter the line as is or you can add more<br>characters to it. You can edit the line by<br>backspacing and typing over old characters. |

When observing output from any 197Bug command, the XON and XOFF characters which are in effect for the terminal port may be entered to control the output, if the XON/XOFF protocol is enabled (default). These characters are initialized to **^S** and **^Q** respectively by 197Bug but may be changed by the user using the **PF** command. In the initialized (default) mode, operation is as follows:

| ^S | (wait)   | Console output is halted.  |

|----|----------|----------------------------|

| ^Q | (resume) | Console output is resumed. |

# **Disk I/O Support**

197Bug can initiate disk input/output by communicating with intelligent disk controller modules over the VMEbus. Disk support facilities built into 197Bug consist of:

- □ Command-level disk operations

- □ Disk I/O system calls (only via one of the TRAP #496 instructions) for use by user programs

- Defined data structures for disk parameters

Parameters such as the:

- □ Address where the module is mapped

- Type of device

- Number of devices attached to the controller module

are kept in tables by 197Bug. Default values for these parameters are assigned at power-up and cold-start reset, but may be altered as described in the section on default parameters, later in this chapter.

#### **Blocks Versus Sectors**

The logical block defines the unit of information for disk devices. A disk is viewed by 197Bug as a storage area divided into logical blocks. By default, the logical block size is set to 256 bytes for every block device in the system. The block size can be changed on a per device basis with the **IOT** command.

The sector defines the unit of information for the media itself, as viewed by the controller. The sector size varies for different controllers, and the value for a specific device can be displayed and changed with the **IOT** command.

When a disk transfer is requested:

- □ The start and size of the transfer is specified in blocks

- □ 197Bug translates this into an equivalent sector specification

- □ Sector specification is passed on to the controller to initiate the transfer

If the conversion from blocks to sectors yields a fractional sector count, an error is returned and no data is transferred.

#### **Device Probe Function**

A device probe with entry into the device descriptor table is done whenever a specified device is accessed. This happens when system calls:

- .DSKRD

- □ .DSKWR

- DSKCFIG

- □ .DSKFMT

- □ .DSKCTRL

or debugger commands:

- 🗅 BH

- 🗆 во

1

- IOP

- D IOT

- □ MAR

- 🗆 MAW

are used.

The device probe mechanism utilizes the SCSI commands **Inquiry** and **Mode Sense**. If the specified controller is non-SCSI, the probe simply returns a status of **device present and unknown**. The device probe makes an entry into the device descriptor table with the pertinent data. After an entry has been made, the next time a probe is done it simply returns with **device present** status (pointer to the device descriptor).

## Disk I/O via 197Bug Commands

These following 197Bug commands are provided for disk I/O. Detailed instructions for their use are found in the *MVME197BUG 197Bug Debugging Package User's Manual*. When a command is issued to a particular controller LUN and device LUN, these LUNs are remembered by 197Bug so that the next disk command defaults to use the same controller and device.

## IOI (Input/Output Inquiry)

The **IOI** command is used to probe the system for all possible CLUN/DLUN combinations and display inquiry data for devices which support it. The device descriptor table only has space for 16 device descriptors. With the **IOI** command, the user can view the table and clear it if necessary.

## IOP (Physical Input/Output to Disk)

The **IOP** command allows the user to:

- Read blocks of data

- Write blocks of data

- □ Format the specified device in a certain way

**IOP** creates a command packet from the arguments specified by the user, and then invokes the proper system call function to carry out the operation.

## IOT (Input/Output Teach)

The **IOT** command allows the user to:

□ Change any configurable parameters

- □ Change device attributes

- □ See the controllers available in the system

#### **IOC (Input/Output Control)**

The **IOC** command allows the user to send command packets as defined by the particular controller directly. **IOC** can also be used to look at the resultant device packet after using the IOP command.

#### **BO (Bootstrap Operating System)**

**BO** reads an operating system or control program from the specified device into memory, and then transfers control to it.

#### **BH (Bootstrap and Halt)**

**BH** reads an operating system or control program from a specified device into memory, and then returns control to 197Bug. It is used as a debugging tool.

## Disk I/O via 197Bug System Calls

All operations that actually access the disk are done directly or indirectly by 197Bug TRAP #496 system calls. (The command-level disk operations provide a convenient way of using these system calls without writing and executing a program.)

The following system calls allow user programs to do disk I/O operations:

| .DSKRD   | Disk read. System call to read blocks from a disk into memory.                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .DSKWR   | Disk write. System call to write blocks from memory onto a disk.                                                                                                        |

| .DSKCFIG | Disk configure. This function allows the user to change<br>the configuration of the specified device.                                                                   |

| .DSKFMT  | Disk format. This function allows the user to send a format command to the specified device.                                                                            |

| .DSKCTRL | Disk control. This function is used to implement any<br>special device control functions that cannot be<br>accommodated easily with any of the other disk<br>functions. |

Refer to the *MVME197BUG 197Bug Debugging Package User's Manual* for information on using these and other system calls.

To perform a disk operation, 197Bug must eventually present a particular disk controller module with a controller command packet which has been especially prepared for that type of controller module. (This is accomplished in the respective controller driver module). A command packet for one type of controller module usually does not have the same format as a command packet for a different type of module. The system call facilities which perform disk I/O operations:

- Accept a generalized (controller-independent) packet format as an argument

- □ Translate it into a controller-specific packet

- □ Send to the specified device

Refer to the descriptions in the *System Calls* chapter in the *MVME197BUG* 197Bug Debugging Package User's Manual for details on the format and construction of these standardized "user" packets.

The packets which a controller module expects to be given vary from controller to controller. The disk driver module for the particular hardware module (on- or off-board) must take the standardized packet given to a trap function and create a new packet which is specifically tailored for the disk drive controller it is sent to. Refer to documentation on the particular controller module for the format of its packets, and for using the **IOC** command.

## **Default 197Bug Controller and Device Parameters**

197Bug initializes the parameter tables for a default configuration of controllers and devices. If the system needs to be configured differently than this default configuration (for example, to use a drive that is different from the default), then the user must change these tables.

There are three ways to change the parameter tables:

- □ Using **BO** or **BH**. When you invoke one of these commands, the configuration area of the disk is read and the parameters corresponding to that device are rewritten according to the parameter information contained in the configuration area. This is a temporary change. If a cold-start reset occurs, then the default parameter information is written back into the tables.

- □ Using **IOT**. You can use this command to manually reconfigure the parameter table for any controller and/or device that is different from

the default. This is also a temporary change and is overwritten if a cold-start reset occurs.

Obtain the source. You may change the configuration files and rebuild 197Bug so that it has different defaults. Changes made to the defaults are permanent until changed again.

## **Disk I/O Error Codes**

197Bug returns an error code if an attempted disk operation is unsuccessful.

## Network I/O Support

The Network Boot Firmware provides the capability to boot the CPU through the ROM debugger using a network (local Ethernet interface) as the boot device.

The booting process is executed in two distinct phases:

- □ The first phase allows the diskless remote node to discover its network identity and the name of the file to be booted

- □ The second phase has the diskless remote node reading the boot file across the network into its memory

The following figure depicts the various modules (capabilities) and the dependencies of these modules that support the overall network boot function. They are described in the following paragraphs.

#### Physical Layer Manager Ethernet Driver

This driver manages/surrounds the Ethernet controller chip or board. Management is in the scope of the reception of packets, the transmission of packets, receive buffer flushing, and interface initialization.

This module ensures that the packaging and unpackaging of Ethernet packets is done correctly in the Boot PROM.

#### **UDP/IP Protocol Modules**

The Internet Protocol (IP) is designed for use in interconnected systems of packet-switched computer communication networks. The Internet protocol provides for transmitting of blocks of data called datagrams (hence User Datagram Protocol, or UDP) from sources to destinations, where sources and destinations are hosts identified by fixed length addresses.

The UDP/IP protocols are necessary for the TFTP and BOOTP protocols. TFTP and BOOTP require a UDP/IP connection.

Figure 1-1. Network Boot Modules

## **RARP/ARP Protocol Modules**

The Reverse Address Resolution Protocol (RARP) basically consists of an identity-less node broadcasting a "whoami" packet onto the Ethernet, and waiting for an answer. The RARP server fills an Ethernet reply packet up with the target's Internet Address and sends it.

The Address Resolution Protocol (ARP) basically provides a method of converting protocol addresses (e.g., IP addresses) to local area network addresses (e.g., Ethernet addresses). The RARP protocol module supports systems which do not support the BOOTP protocol (next paragraph).

#### **BOOTP Protocol Module**

The Bootstrap Protocol (BOOTP) basically allows a diskless client machine to discover its own IP address, the address of a server host, and the name of a file to be loaded into memory and executed.

#### **TFTP Protocol Module**

The Trivial File Transfer Protocol (TFTP) is a simple protocol to transfer files. It is implemented on top of the Internet User Datagram Protocol (UDP or Datagram) so it may be used to move files between machines on different networks implementing UDP. The only thing it can do is read and write files from/to a remote server.

#### **Network Boot Control Module**

The "control" capability of the Network Boot Control Module is needed to tie together all the necessary modules (capabilities) and to sequence the booting process. The booting sequence consists of two phases: the first phase is labeled "address determination and bootfile selection" and the second phase is labeled "file transfer". The first phase will utilize the RARP/BOOTP capability and the second phase will utilize the TFTP capability.

#### Network I/O Error Codes

197Bug returns an error code if an attempted network operation is unsuccessful. Refer to Appendix H of the *MVME197BUG 197Bug Debugging Package User's Manual* for an explanation of network I/O error codes.

# **Multiprocessor Support**

The MVME197 dual-port RAM feature makes the shared RAM available to remote processors as well as to the local processor. This can be done by either of the following two methods. Either method can be enabled/disabled by the **ENV** command as its Remote Start Switch Method.

## Multiprocessor Control Register (MPCR) Method

A remote processor can initiate program execution by the local MVME197 MPU which is running the debugger by issuing a remote **GO** command using the Multiprocessor Control Register (MPCR). The MPCR, located at shared RAM location of \$3000 offset from the base address of the debugger RAM work area (normally \$0), contains one of two words used to control communication between processors.

The MPCR contents are organized as follows:

| \$3000 | * | N/A | N/A | N/A | (MPCR) |

|--------|---|-----|-----|-----|--------|

|--------|---|-----|-----|-----|--------|

The status codes stored in the MPCR are of two types:

- Status set (by the MVME197 MPU)

- Commands set (by the remote processor)

The status codes that may be returned from the MVME197 MPU are:

| HEX   | 0 | (HEX 00) | Wait. Initialization not yet complete.                |

|-------|---|----------|-------------------------------------------------------|

| ASCII | R | (HEX 52) | Ready. The firmware monitor is watching for a change. |

| ASCII | E | (HEX 45) | Code pointed to by the MPAR address is executing.     |

The user can only program FLASH memory by the MPCR method. Refer to the **.PFLASH** system call in the *MVME197BUG 197Bug Debugging Package User's Manual* for a description of the FLASH memory program control packet structure.

The command codes that may be set by the remote processor are:

| ASCII | G | (HEX 47) | Use Go Direct ( <b>GD</b> ) logic specifying the MPAR address.                                         |

|-------|---|----------|--------------------------------------------------------------------------------------------------------|

| ASCII | Р | (HEX 50) | Program FLASH memory. The MPAR is set<br>to the address of the FLASH memory<br>program control packet. |

| ASCII | В | (HEX 42) | Install breakpoints using the Go $(\mathbf{G})$ logic.                                                 |

The Multiprocessor Address Register (MPAR), located in shared RAM location of \$3004 offset from the base address of the debugger RAM work area, contains the second of two words used to control communication between processors. The MPAR contents specify the address at which execution for the remote processor is to begin if the MPCR contains a G or B.

The MPAR is organized as follows:

| \$3004 | * | * | * | * | (MPAR) |

|--------|---|---|---|---|--------|

|--------|---|---|---|---|--------|

At power up, the debug monitor self-test routines initialize RAM, including the memory locations used for multi-processor support (\$3000 through \$3007).